服务热线 13823541376

深圳市谷易电子有限公司

联系电话:13823541376

联系人:兰小姐

邮箱:sales@goodesocket.com

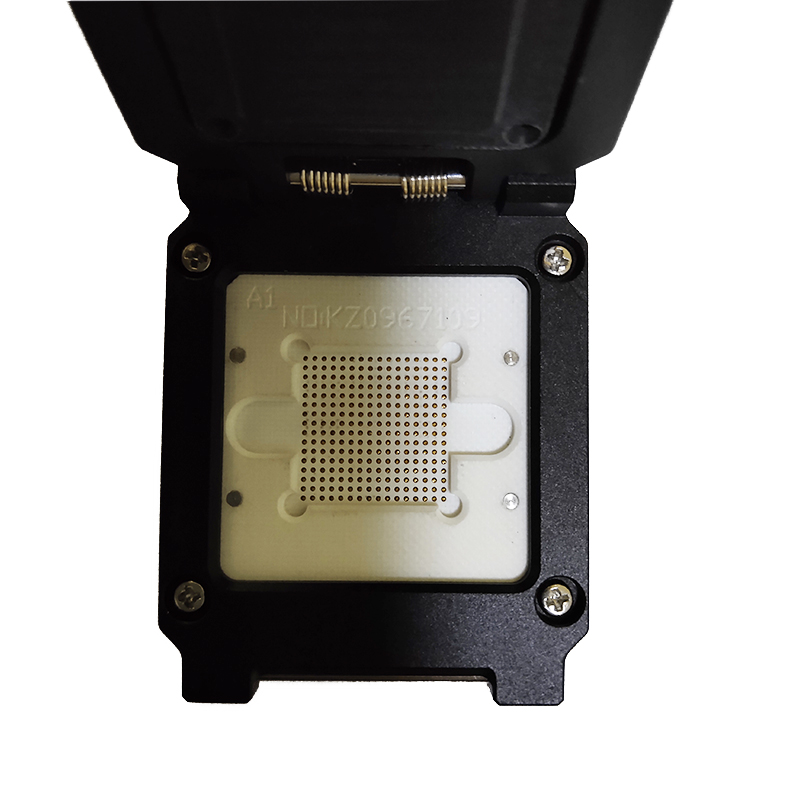

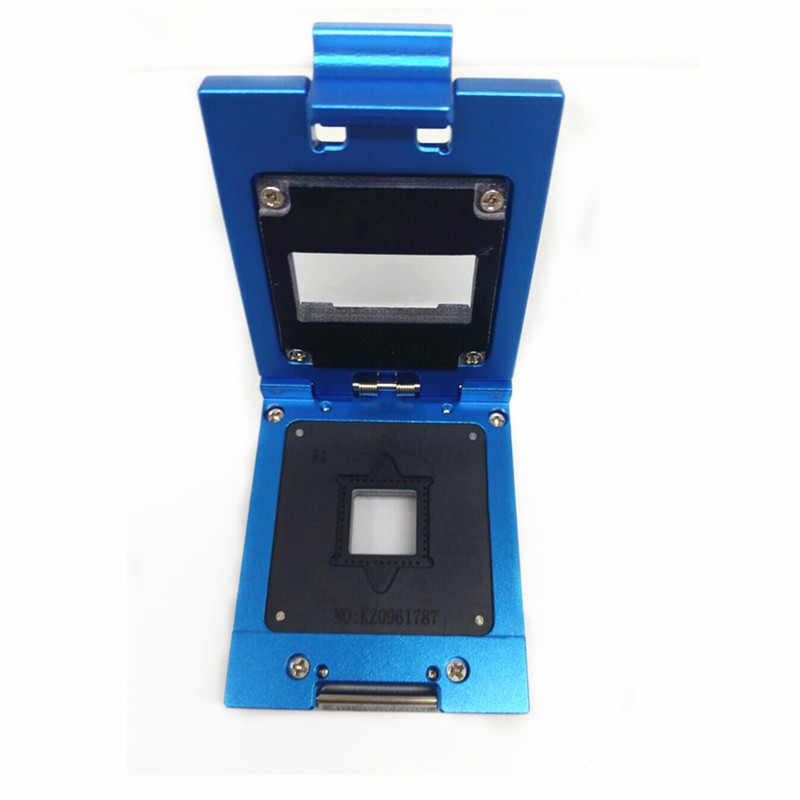

主营产品:定制测试座、老化测试座、弹片微针模组、memory测试座、测试夹具、BGA老化测试、QFN老化测试、Flash闪存测试、编程烧录座

发表时间:2021-07-30 16:33:20浏览量:1710【小中大】

良率和可靠性是影响半导体行业成本和利润的两个关键因素。压力测试是一种基于应用高于通常水平的压力的技术,以加速电子设备的退化并提高产量和可靠性。压力测试的标准工业方法之一是高温老化。这项工作提出了一种用于动态老化的全扫描电路 ATPG。提议的 ATPG 方法的目标是生成能够强制转换到全扫描电路的每个节点的测试模式,以保证动态老化测试期间应力的均匀分布。

一、简介

良率和可靠性是影响半导体行业成本和利润的两个关键因素 :

[1] 、有大量物理故障机制会影响电子元件的可靠性。其中,常见的有TDDB(Time Dependent Dielectric Breakdown)、热载流子老化、电迁移等。此外,某些制造步骤会引起应力,从而导致潜在损坏,从而缩短器件寿命。

[2]、压力测试是一种基于应用高于通常水平的压力以加速电子设备退化的技术。这种筛选过程背后的想法是加速设备的使用寿命,并让它以超出所谓的婴儿死亡率区域的故障率开始正常运行。

[3]、压力测试的标准工业方法是高温老化和高压筛选老化已被证明在不同程度上对几乎所有导致永久性故障的电路和组装原因都有效。特别是老化筛选能够降低产品在早期现场寿命期间的故障率,在此期间,总体成本和周转时间是值得关注的。添加的制造成本可能占总产品成本的 5% 至 40%,具体取决于老化时间、IC 质量和产品复杂性

[4]、必须仔细注意老化应力的设计,以确保准确发现潜在缺陷,另一方面,不会对剩余设备的使用寿命产生不利影响。

特别是,在所谓的动态老化(见第 2 节)的情况下,能够在被测电路的所有部分以统一方式强制转换的测试模式的设计是一个悬而未决的问题。

这项工作提出了一种用于动态老化的全扫描电路 ATPG。提议的 ATPG 的目标是生成能够强制转换到全扫描电路的每个节点的测试模式,以保证动态老化测试期间应力的均匀分布。

此外,我们的方法试图平衡强制进入电路的转换,以避免器件的部分应力过大并可能损坏它。

2.老化测试的问题

老化是一种筛选方法,用于利用加速老化消除完全加工的微电子部件中的缺陷组件。这种筛选是通过施加压力操作条件获得的。

主要我们可以区分三种类型的老化:

· 简单状态老化包括施加偏压和温度并在老化前后进行元件测试。输入和输出引脚开路,仅连接电源引脚。这种简单的电路板设计允许以低成本并行对多个部件施加应力。缺点是不是电路的所有节点都被激励,并且在老化过程中没有反馈,这导致所有老化类型的逃逸率最高;

· 动态老化解决了并非所有节点都受到压力的潜在问题。除了升高的电压和温度之外,外部信号也会施加到所有芯片并联的输入引脚。这种技术需要在老化条件下具有完整的产品功能,但可以提高老化效率,同时成本仍然适中,并且很容易实现许多零件的平行应力。在老化期间仍然没有来自任何芯片的反馈可用。通过监控的动态老化实现了进一步的改进。在这种情况下,会执行一些有限的响应监控。根据监测的程度,平行应力受到限制,设备变得更加昂贵。然而,逃逸率降低了;

· 最先进的老化类型是 TDBI(老化期间的测试)。它对每个单独的芯片应用全功能测试模式和全响应监控。优点是可以确定准确的故障时间和特征以及设备或接触问题。因此,可以最大限度地减少老化泄漏,并且可以回收未暴露于老化电压的芯片。每个芯片的单独监控限制了可以在一个老化板上施加压力的部件数量,所需的设备使这种类型的老化通常非常昂贵。

在这项工作中,我们专注于动态老化,这是工业中最常见的一种 。老化逃逸的主要原因之一是缺少老化模式,这使得并非所有节点都受到足够的压力。

通常,这些模式由随机生成的模式或为验证和验证电路功能的正确性而生成的功能模式组成。在动态老化中,由于不考虑电路的响应,测试模式的目标是在高压和高温条件下对器件施加压力。在这种情况下,对电路的所有部分施加均匀应力的能力是减少老化和提高最终产品可靠性的关键因素。

这项工作的目标是自动生成测试模式,能够在被测电路的所有节点中以统一的方式执行所有可能的转换(从 0 到 1,以及从 1 到 0)。我们专注于全扫描时序电路。这项工作的动机来自观察到随机和功能模式(例如,卡在模式上),电路的某些网络在测试期间通常比其他网络承受更大的压力。

对于转换故障的通用 ATPG,我们不需要在测试期间观察电路输出,但我们需要在扫描扫描链中的模式时考虑组合节点执行的转换。

3.自动测试模式生成

我们的自动测试模式生成算法尝试生成一个测试模式,该测试模式能够在被测设备 (DUT) 的每个节点中强制进行几次转换(0 →1 和 1→0)。我们将专注于全扫描电路,为了简单起见,我们将考虑单个扫描链。无论如何,该方法是通用的并且可以应用于具有多个扫描链的电路。

在测试期间,全扫描电路可以在两种不同的模式下运行:(i) 扫描模式和 (ii) 捕获模式。在扫描模式下,测试模式被串行加载(扫描)到扫描链的触发器中,以便将存储元件初始化为给定值并计算下一个状态值。在捕获模式下,应用时钟周期以将模式结果再次存储到触发器中,触发器的值可以通过扫描其内容来读取。

在传统的 ATPG 中,例如固定故障的模式生成,ATPG 不需要考虑在扫描阶段期间电路的组合部分会发生什么。在这种情况下,连接到扫描链的逻辑门根据触发器中临时扫描的值执行转换。不考虑这些转换,因为除非应用时钟周期(捕获模式),否则它们不会影响电路的同步行为。

在动态老化的情况下,情况完全不同。需要考虑强制在电路节点上的所有转换,因为它们对电路的总应力有贡献。提议的 ATPG 通过生成测试模式来考虑这个问题,这些测试模式考虑了在扫描阶段强制进入电路的转换。建议的方法在以下小节中详细描述。

3.1.ATPG算法

ATPG 算法是所提出的模式生成过程的核心部分。这是一个迭代过程,它跟踪 DUT 的每个节点执行的转换,并在每次迭代时尝试生成新的测试模式 (TP),以在电路的一个节点上强制执行新的转换。为了实现过渡的均匀分布

在线咨询

在线咨询

扫一扫关注官方微信

13823541376

13823541376