服务热线 13823541376

深圳市谷易电子有限公司

联系电话:13823541376

联系人:兰小姐

邮箱:sales@goodesocket.com

主营产品:定制测试座、老化测试座、弹片微针模组、memory测试座、测试夹具、BGA老化测试、QFN老化测试、Flash闪存测试、编程烧录座

发表时间:2024-07-01 16:30:08浏览量:827【小中大】

CMOS(互补金属氧化物半导体)工艺依然占据着主导地位,并驱动着微电子行业的快速进步。为了应对日益严格的市场需求和缩减晶体管尺寸带来的技术挑战,业界不断探索新的技术路径。CFET(垂直堆叠式场效应晶体管)作为一种创新的晶体管结构,正在成为行业内的研究热点。

1. CMOS CFET与传统FET的差异

传统的FET(场效应晶体管)结构按照平面几何进行设计,其源极和漏极触点在同一平面上,这种结构随着制程节点的微缩逐渐显露出某些局限性,根据谷易电子CMOS CFET test socket工程师介绍:比如短沟道效应、电流泄漏等问题。而CFET则通过垂直堆叠的方式,将n型和p型FET堆叠在一起,在纵向上形成多个晶体管单元,这样不仅有效地利用了空间,还增强了器件的性能。

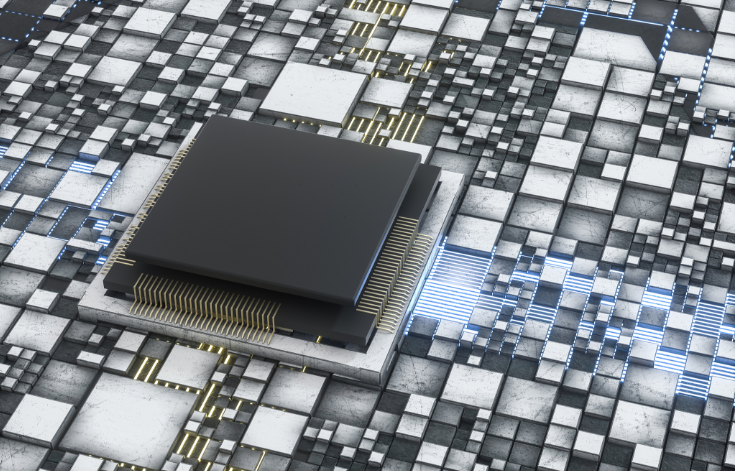

2. 堆叠底部和顶部源极/漏极触点的设计

CFET的设计核心是如何高效地实现垂直堆叠,同时保证每个堆叠层之间的电气连接和隔离。堆叠底部和顶部源极/漏极触点的设计对CFET的性能起着至关重要的作用。通过优化这些触点的设计,CFET可以达到以下几个目标:

2.1 减少电阻和电感

触点的设计必须确保在不同层之间提供低阻抗的连接路径,同时也要尽量避免高频信号传输时产生的感应和寄生效应。现代制造工艺通过先进的材料如铜和钨以及纳米级的精细加工技术来降低这些阻抗。

2.2 提高热管理能力

垂直堆叠结构使得晶体管密度大大增加,这必然会带来更高的热密度。如果不解决这个问题,过高的温度会显著影响器件的性能和可靠性。为此,堆叠触点的材料需要具备良好的导热性能,同时还要考虑到内部结构的热管理设计。

2.3 改进电气隔离效果

由于不同层之间可能存在不同类型的FET,需要有效地进行电气隔离以防止漏电和干扰。通常,这个问题通过精密的介电材料和多层栅极绝缘体技术来解决。

3. CMOS CFET在半导体行业中的应用

3.1 在高速计算中的应用

由于CFET的高密度和低功耗特性,其在高速计算领域具有巨大潜力。例如,CFET可以用来构建更为复杂的逻辑电路,提高整体计算性能。

3.2 在移动设备中的应用

移动设备的性能和续航能力一直是消费者关注的焦点。CFET的低能耗和高效散热技术可以显著延长设备的电池寿命,同时提升整体性能,成为下一代移动设备的理想选择。

3.3 在物联网中的应用

物联网设备通常需要具备低功耗和高性能的特点,以确保长时间稳定运行。CFET在这方面表现优秀,我们可以预见其在智能家庭设备、工业传感器等领域中的广泛应用。

4. 堆叠底部和顶部源极/漏极触点的制造工艺挑战

4.1 纳米级精度的加工技术

根据谷易电子CMOS CFET test socket工程师介绍:堆叠触点的设计和制造要求达到纳米级别的精度,以确保每个连接和隔离都能准确实现。当前的光刻技术已经接近物理极限,因此需要寻找更高精度的加工手段,比如电子束光刻。

4.2 材料选择与兼容性问题

触点材料的选择不仅影响电气性能,还需考虑其与其他材料的兼容性及长期稳定性。例如,铜虽然具有良好的导电性能,但会在高温下氧化,需要外层添加保护材料。

4.3 高效的散热管理

散热问题在堆叠结构中尤为突出,必须开发出更加高效的散热材料和设计方法,例如新型的热界面材料和更具导热性的基板。

5. 堆叠触点技术的未来展望

CFET中的堆叠底部和顶部源极/漏极触点技术显现出巨大的发展潜力。未来,随着纳米加工技术的进一步突破,与之相关的新材料、新工艺将成熟,这将大大推动CFET的广泛应用。

5.1 更高效的量产技术

如何将这种高精度的堆叠触点技术应用于大规模量产,是业界需要解决的一个重要问题。自动化生产线、智能制造技术以及AI算法优化的引入,将可能成为解决这一难题的重要手段。

5.2 材料科学的进展

新材料的研发和应用直接关系到CFET触点技术的性能提升。例如,二维材料,如石墨烯和过渡金属二硫化物,具有出色的电学和热学特性,可能成为未来CFET触点的理想材料。

根据谷易电子CMOS CFET test socket工程师介绍:CMOS CFET中的堆叠底部和顶部源极/漏极触点技术,凭借其在电气性能、散热管理和结构设计方面的优势,推动了半导体技术的发展。尽管面临许多技术挑战,但不断创新的材料科学和制造工艺将使得这一技术在未来的电子设备中发挥重要作用。

测试座能够精确对接CFET器件的源极/漏极触点,进行静态和动态的电性能测试。对于逻辑门电路来说,电路的响应速度、功耗和稳定性是关键指标,能够有效评估器件在这些方面的表现。

低功耗和高速度的验证:

CMOS CFET器件在逻辑门电路中的优势包括低静态功耗和高速操作。根据谷易电子CMOS CFET test socket工程师介绍:CMOS cfet test测试座能够验证这些优势,确保器件在实际应用中能够达到设计要求的功耗和速度

在线咨询

在线咨询

扫一扫关注官方微信

13823541376

13823541376