服务热线 13823541376

深圳市谷易电子有限公司

联系电话:13823541376

联系人:兰小姐

邮箱:sales@goodesocket.com

主营产品:定制测试座、老化测试座、弹片微针模组、memory测试座、测试夹具、BGA老化测试、QFN老化测试、Flash闪存测试、编程烧录座

发表时间:2025-04-14 14:50:14浏览量:606【小中大】

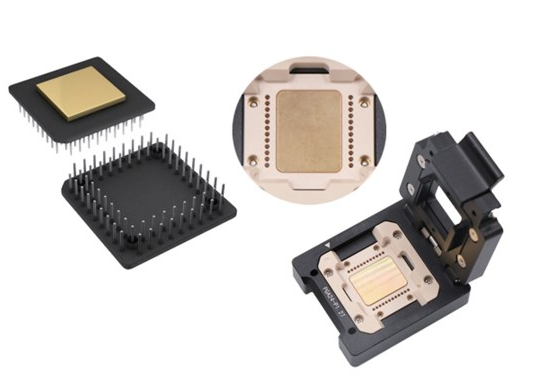

PGA(Pin Grid Array,针栅阵列)封装凭借其高引脚密度、优异的机械稳定性及散热性能,广泛应用于高性能CPU、FPGA及服务器芯片等场景。然而,其复杂的针脚布局与高可靠性需求对测试技术提出了严峻挑战。本文以导通测试、功能性测试、高性能测试、可靠性测试、逻辑测试为核心,结合谷易电子PGA芯片测试座、老化座及烧录座的关键技术,系统解析测试方法、标准与实践应用,助力国产半导体测试技术的突破。

一、PGA封装特性与核心应用场景

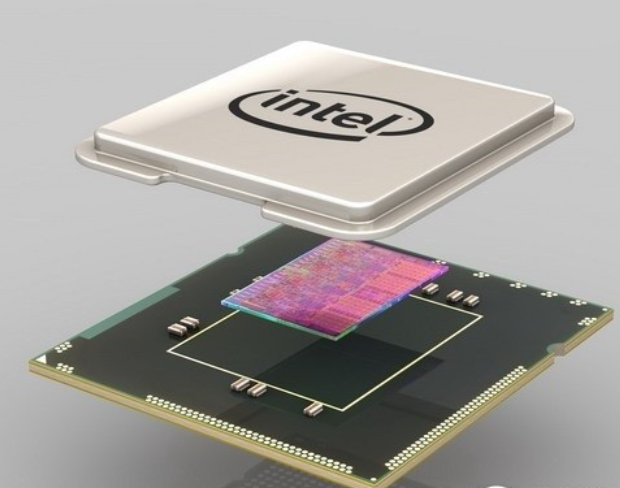

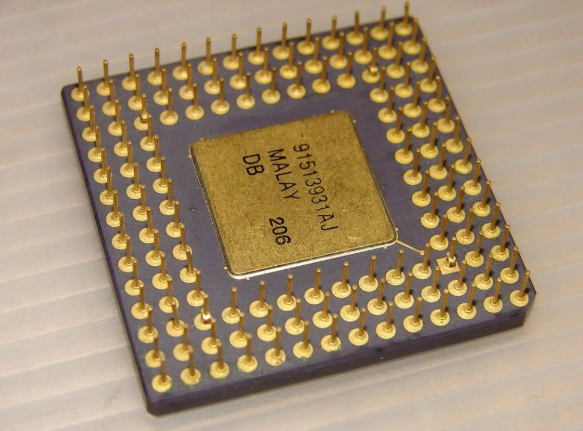

1.封装结构特点

针脚布局:引脚呈阵列式排列(如37×37矩阵),间距通常为2.54mm或1.27mm(高密度型),引脚数可达500+。

散热设计:顶部集成金属散热盖或导热柱,热阻(θJA)低至10℃/W,适配大功率芯片。

应用场景:

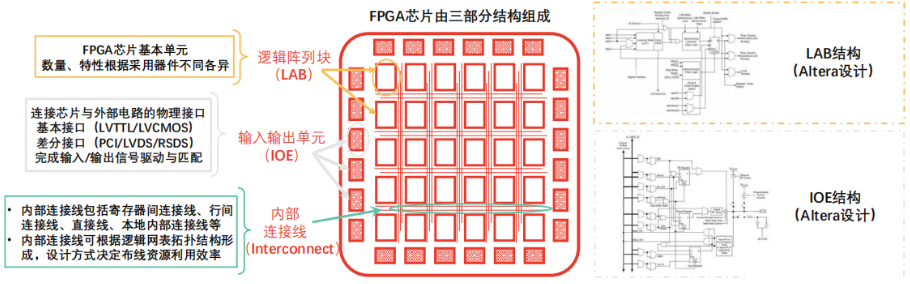

高性能计算:服务器CPU(如Intel Xeon系列)、FPGA(如Xilinx Virtex)。

工业控制:PLC主控芯片、高精度ADC/DAC模块。

二、核心测试项与标准

1.导通测试(Continuity Test)

定义:验证PGA芯片引脚与PCB测试座的电气连通性,排除开路、短路及虚焊缺陷。

测试方法:

四线法:精度±0.1mΩ,检测电源与接地引脚的接触电阻(≤50mΩ)。

飞针测试:通过多探针快速扫描引脚连通性,效率达每秒数千点,适配小批量验证。

标准要求:依据IPC-A-610,引脚弯曲度需≤0.1mm,接触电阻波动<5%。

2.功能性测试(Functional Test)

定义:验证芯片在额定工况下的逻辑功能与协议兼容性,如PCIe 5.0、DDR5接口性能。

测试方法:

ATE(自动测试设备):集成多通道电源与协议引擎,支持并行测试,吞吐量>500片/小时。

协议分析仪:验证64GT/s(PCIe 5.0)信号的眼图张开度(≥0.3UI)与误码率(BER<10^-12)。

谷易电子PGA芯片测试座:采用同轴探针结构,寄生电感<0.1nH,支持40GHz高频信号测试,适配服务器CPU验证。

3.高性能测试(High-Performance Test)

定义:评估芯片在极限负载下的计算能力、功耗效率及散热性能。

测试项与测试座:

动态功耗测试:通过功率分析仪测量TDP(如300W),确保满载电流波动<5%。

热阻分析:红外热成像仪监测结温分布,验证θJA≤15℃/W(JESD51-14标准)。

频率稳定性:使用示波器捕获时钟抖动(<1ps RMS),确保PLL锁相环性能达标。

测试条件:环境温度25℃±1℃,湿度40-60% RH,电源纹波<50mV。

4.可靠性测试(Reliability Test)

定义:模拟极端环境与长期使用工况,验证芯片寿命与失效阈值。

测试项与标准:

HTOL(高温工作寿命测试):125℃下运行1000小时,参数漂移<10%(AEC-Q100标准)。

温度循环测试:-55℃↔125℃循环1000次,引脚剪切力保持≥5N(MIL-STD-883标准)。

振动测试:20G加速度,3轴振动,持续96小时,验证机械结构稳定性。

谷易电子PGA芯片老化座:碳纤维基板与殷钢复合结构(CTE 4.5ppm/℃),宽温域(-55℃~155℃)下对位精度±5μm,适配车规级FPGA测试。

5.逻辑测试(Logic Test)

定义:通过边界扫描与静态时序分析,验证内部电路逻辑正确性。

测试方法:

JTAG边界扫描:覆盖率≥95%,检测开路/短路故障(IEEE 1149.1标准)。

静态时序分析(STA):验证关键路径延迟(Setup Time≤0.5ns,Hold Time≥0.2ns)。

谷易电子PGA芯片烧录座:集成边界扫描链与CRC校验算法,支持10Gbps速率烧录,良率>99.99%。

三、谷易电子PGA芯片测试座的关键技术突破

1.高密度探针设计

双曲面接触头:采用镀金铍铜探针,接触电阻<20mΩ,插拔寿命>50万次,适配PGA 1.27mm高密度引脚。

弹性压力控制:单针压力30g±5g,支持引脚高度公差±0.1mm,避免过度下压导致变形。

2.宽温域兼容性

碳纤维-殷钢基板:热膨胀系数(CTE)匹配陶瓷PGA封装,高温下无接触偏移,确保-55℃~175℃稳定测试。

热电偶集成:实时监测芯片结温,精度±0.5℃,支持HTOL自动化控制。

3.智能化测试整合

多协议兼容接口:支持PCIe 5.0、CXL 2.0协议栈,适配服务器与AI芯片测试需求。

AI驱动优化:机器学习算法动态补偿探针磨损,误判率降低至0.01%,延长设备寿命。

四、应用场景与国产化实践

1. 服务器CPU测试

场景痛点:Intel Xeon系列CPU需验证64通道PCIe 5.0接口的信号完整性。

谷易方案:多通道同轴芯片测试座支持40GHz带宽,眼图张开度>0.3UI,误码率<10^-12,适配HVM量产。

2. 车规级FPGA芯片老化验证

场景痛点:Xilinx车规FPGA需通过-40℃~125℃温度循环测试。

谷易方案:芯片老化座集成热电偶与电压监控模块,实时追踪结温漂移,故障定位至引脚级。

五、未来趋势与挑战

1.高频化与三维集成:针对5G毫米波(120GHz)与3D封装,开发垂直探针阵列与TSV互连检测技术。

2.智能化预测性维护:通过大数据分析预测探针寿命,动态优化测试参数,减少停机时间。

3.绿色测试技术:推动无铅焊料与低功耗测试设备,降低碳足迹。

PGA封装芯片的全面测试技术是保障其在高性能计算与工业控制领域可靠性的核心。谷易电子通过高密度探针设计、宽温域兼容性与智能化测试生态,为国产服务器CPU与车规芯片提供了高精度验证方案。未来,随着异构集成与AI技术的普及,测试设备将向更高频、更智能的方向演进,推动中国半导体产业链向高端化突破。

(注:本文技术参数参考自JEDEC、AEC-Q标准及谷易电子公开技术资料。)

在线咨询

在线咨询

扫一扫关注官方微信

13823541376

13823541376