服务热线 13823541376

深圳市谷易电子有限公司

联系电话:13823541376

联系人:兰小姐

邮箱:sales@goodesocket.com

主营产品:定制测试座、老化测试座、弹片微针模组、memory测试座、测试夹具、BGA老化测试、QFN老化测试、Flash闪存测试、编程烧录座

发表时间:2025-12-08 10:17:53浏览量:1079【小中大】

在半导体测试链路中,芯片测试座并非独立存在的器件,其核心价值的实现,完全依赖于与芯片pin脚的精准匹配,而LAYOUT封装图纸则是连接二者的"技术桥梁"。芯片pin脚作为信号传输的"出入口",测试座作为临时连接的"转接枢纽",二者的适配精度直接决定测试数据的真实性与可靠性。谷易电子深耕芯片测试座领域十余年,在pin脚适配技术与LAYOUT封装图纸优化方面积累了丰富经验,其实践案例为行业呈现了从设计到应用的完整技术逻辑。

芯片测试座与pin脚的关系,本质上是"精准对接"与"稳定传输"的双重诉求。pin脚作为芯片与外部电路的接口,承担着电源供给、信号交互、数据传输等核心功能,其数量、排布方式、间距、材质及电气参数,直接定义了测试座的设计标准。一款合格的测试座,

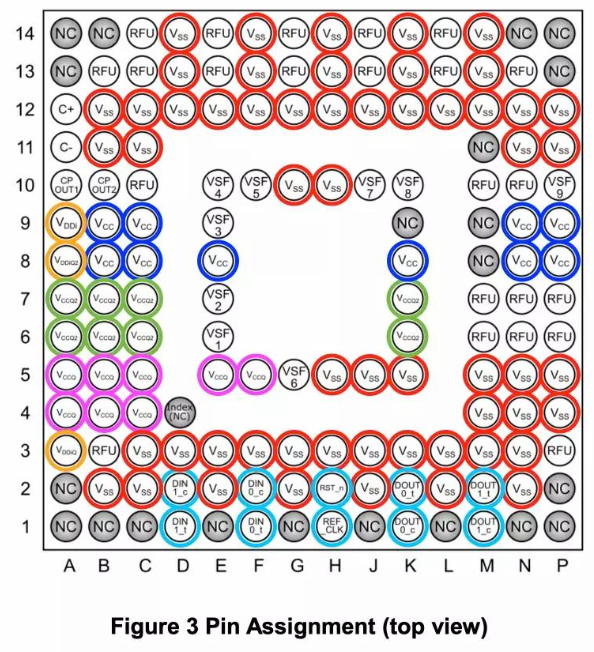

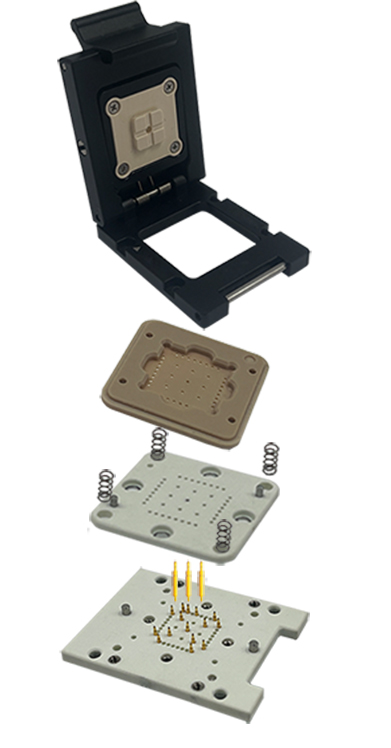

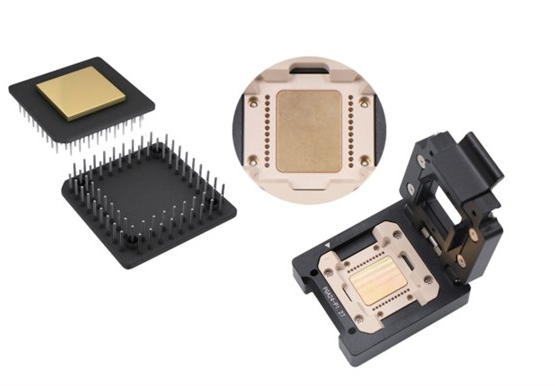

首先要实现与pin脚的物理精准适配——针脚位置需与pin脚坐标完全重合,针脚直径需匹配pin脚的接触面积,针脚弹性需在保证接触压力的同时避免损伤pin脚。谷易电子针对QFP封装芯片的pin脚密集特性(部分型号pin脚间距仅0.4mm),研发出"微针阵列定位技术",通过激光蚀刻工艺将测试座针脚定位误差控制在±0.01mm以内,彻底解决了细间距pin脚易出现的接触偏移问题。

除物理适配外,电气特性的匹配是二者关系的核心维度。芯片pin脚的阻抗特性、电流承载能力、信号传输速率,均需通过测试座的针脚设计实现精准承接。例如,高速信号pin脚对测试座的寄生电容、电感要求极高,若测试座针脚的阻抗与pin脚不匹配,会导致信号反射、延迟等问题,直接影响测试结果的准确性。

谷易电子针对5G通信芯片的高速信号pin脚,在测试座设计中引入"阻抗匹配优化方案",通过在LAYOUT封装图纸中增加阻抗匹配网络,将测试座针脚的特征阻抗稳定在50Ω±5%范围内,完美适配芯片pin脚的信号传输需求,使高速信号测试的误码率降至10⁻¹²以下。

LAYOUT封装图纸在这一适配过程中,扮演着"技术蓝图"的关键角色,其设计质量直接决定测试座与pin脚的适配效果。一份完整的测试座LAYOUT封装图纸,需包含pin脚坐标映射、针脚排布拓扑、信号路径规划、散热结构设计、定位基准标注等核心要素。谷易电子建立了"芯片参数-封装图纸-测试座设计"的联动体系,在获取芯片pin脚参数后,

首先通过仿真软件构建pin脚信号传输模型,再基于模型优化LAYOUT封装图纸中的针脚排布与信号路径。例如,针对车规MCU芯片的多电源pin脚与信号pin脚交织排布的特点,谷易电子在封装图纸中采用"电源区域与信号区域隔离设计",将电源针脚集中布置并增加接地屏蔽层,有效避免了电源噪声对信号pin脚测试的干扰。

在具体适配应用中,谷易电子的LAYOUT封装图纸设计充分体现了场景化思维。在工业控制芯片测试领域,某客户的芯片pin脚存在"高低压混用"特性(部分pin脚承载220V高压,部分传输微弱控制信号),传统封装图纸设计易出现信号串扰。谷易电子在图纸设计中采用"立体分层布局",将高压针脚与低压信号针脚在垂直方向错开排布,同时在LAYOUT中增加高压隔离栏与信号屏蔽线,通过这一优化,测试座的高压绝缘性能达到1000V AC/分钟,信号串扰衰减量超过80dB,完全满足客户需求。

针对消费电子领域芯片pin脚小型化、集成化的趋势,谷易电子创新推出"模块化LAYOUT封装方案"。该方案将测试座的针脚模块、散热模块、定位模块在图纸中进行标准化设计,针对不同pin脚数量的芯片(从8pin到256pin),可快速调整模块组合,大幅缩短测试座的研发周期。

以某智能手机处理器芯片为例,传统封装图纸设计需2周时间,采用谷易电子的模块化方案后,仅需3天即可完成适配图纸设计,且测试座的针脚与芯片pin脚的接触成功率提升至99.99%。

值得注意的是,谷易电子在LAYOUT封装图纸设计中,还融入了可制造性与可维护性考量。图纸中详细标注了测试座针脚的更换基准与维护路径,针对易磨损的pin脚对应测试针脚,在图纸中设计了"快拆结构",使测试座的维护成本降低40%,使用寿命延长至1.5万次以上。同时,图纸采用标准化数据格式,可直接对接全自动贴装设备,实现测试座与PCB板的精准焊接,提升批量生产效率。

芯片测试座与pin脚的适配关系,是半导体测试技术的基础命题,而LAYOUT封装图纸则是破解这一命题的关键工具。谷易电子通过对pin脚特性的深度解析、封装图纸的精准设计,以及场景化的技术优化,不仅实现了测试座与各类芯片pin脚的高效适配,更推动了芯片测试环节的稳定性与经济性提升。在半导体产业向先进制程迈进的背景下,这种"以pin脚需求为核心,以封装图纸为支撑"的设计理念,将为芯片测试座的技术创新提供重要方向,助力我国半导体测试产业实现更高水平的自主可控。

在线咨询

在线咨询

扫一扫关注官方微信

13823541376

13823541376