服务热线 13823541376

深圳市谷易电子有限公司

联系电话:13823541376

联系人:兰小姐

邮箱:sales@goodesocket.com

主营产品:定制测试座、老化测试座、弹片微针模组、memory测试座、测试夹具、BGA老化测试、QFN老化测试、Flash闪存测试、编程烧录座

发表时间:2025-03-18 16:13:05浏览量:2635【小中大】

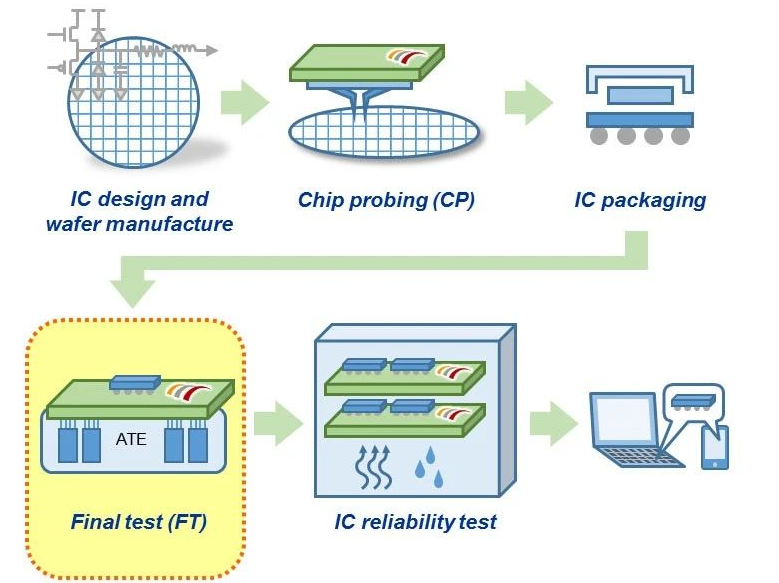

CP测试(Chip Probing,晶圆测试)与FT测试(Final Test,成品测试)作为半导体制造流程中的核心环节,直接影响芯片的良率与可靠性。本文将从CP/FT的定义、测试项、方法及参数标准展开分析,并结合谷易电子的测试座、老化座等案例探讨其技术实现。

一、CP测试与FT测试的定义与核心目标

1. CP测试

CP测试在晶圆制造完成后、封装前进行,通过探针接触晶圆上的裸片(Die)进行电气性能检测,目标是筛选出不良品以节省后续封装成本。例如,SiC晶圆因工艺复杂性高,CP测试可提前剔除击穿电压(BVdss)不达标的裸片,避免封装资源浪费。

技术挑战:探针卡设计需适配高功率SiC芯片的大电流需求(如导通电阻Rdson测试),且需避免多Die并行测试时的信号干扰。

2. FT测试

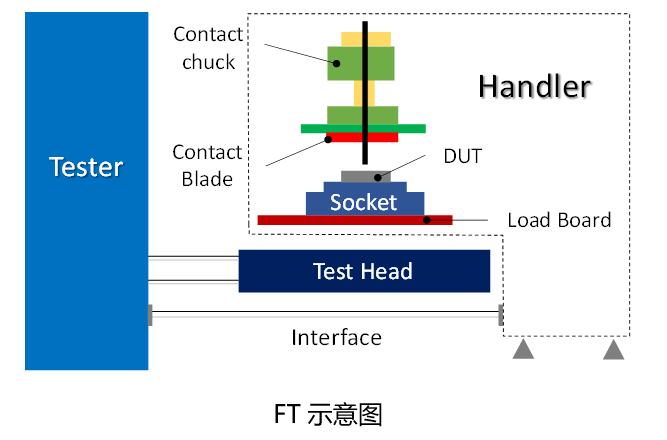

FT测试在封装完成后进行,验证芯片在真实环境下的功能与可靠性。例如,GaN功率模块需在高温(160℃以上)下进行三温测试(常温、低温、高温),确保其高频开关性能稳定。

技术难点:封装引入的寄生电感可能影响高频参数(如开关时间Ton/Toff),需通过低电感测试插座(Socket)提升测试精度。

二、CP与FT的测试项与方法对比

| 测试类别 | CP测试核心项 | FT测试核心项 | 测试方法 |

|--------------|-----------------------------------|-----------------------------------|------------------------------------------------------------------------------|

| 电气参数 | 阈值电压(Vt)、导通电阻(Rdson)、漏电流(Igss) | 电源电流(Idd)、待机功耗、击穿电压(VBR) | CP:探针台+高精度SMU(源测量单元)<br>FT:测试机(Tester)+负载板(Loadboard) |

| 功能验证*| SCAN测试(逻辑功能)、Boundary SCAN(管脚连通性) | 功能测试(逻辑运算)、高速接口验证(如PCIe/DDR) | CP:基于BIST(内建自测)的存储器测试<br>FT:动态信号完整性测试(如眼图分析) |

| 环境测试| 无(受限于探针电流与温度范围) | 温度循环(-55℃~250℃)、高温老化(HTOL) | FT:高低温测试箱+自动化Handler(分选机) |

| 特殊测试 | RF模块基础功能验证 | RF性能深度测试(如谐波失真、噪声系数) | CP:射频探针卡+矢量网络分析仪<br>FT:射频测试座+信号发生器/分析仪 |

三、测试参数标准与关键技术要求

1. CP测试参数标准

导通电阻(Rdson):SiC MOSFET需控制在mΩ级,测试时需采用脉冲法避免自热效应。

击穿电压(BVdss):对SiC器件要求≥1200V,测试电压需覆盖额定值的1.2倍。

漏电流(Igss):GaN HEMT需低于1μA,测试环境需严格屏蔽电磁干扰。

2. FT测试参数标准

高温开关损耗:GaN模块在150℃下开关损耗需比常温增加≤10%。

三温测试一致性:SiC模块在-40℃/25℃/175℃下的导通电阻偏差需<5%。

封装可靠性:通过HAST(高加速温湿度测试)验证封装抗湿气渗透能力,湿度要求85%RH@130℃。

四、谷易电子IC/芯片测试座解决方案案例

谷易电子针对SiC/GaN的高压、高频特性,开发了适配CP/FT测试的全套硬件方案:

1. 高精度CP探针卡

采用钨铜合金探针,支持500A大电流测试,接触电阻<5mΩ,适用于SiC MOSFET的Rdson批量检测[citation:用户历史案例]。

配备主动冷却系统,避免高功率测试时探针温升导致的参数漂移。

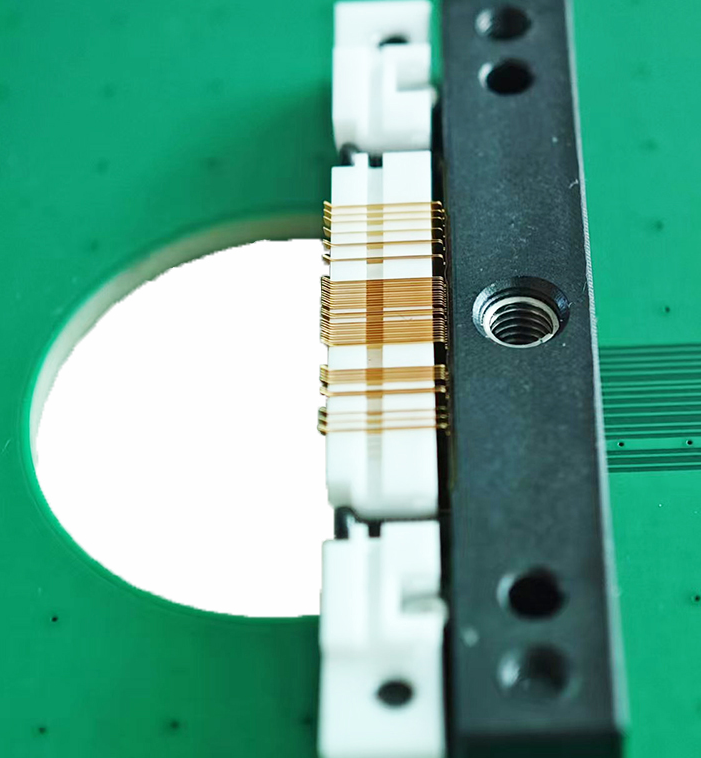

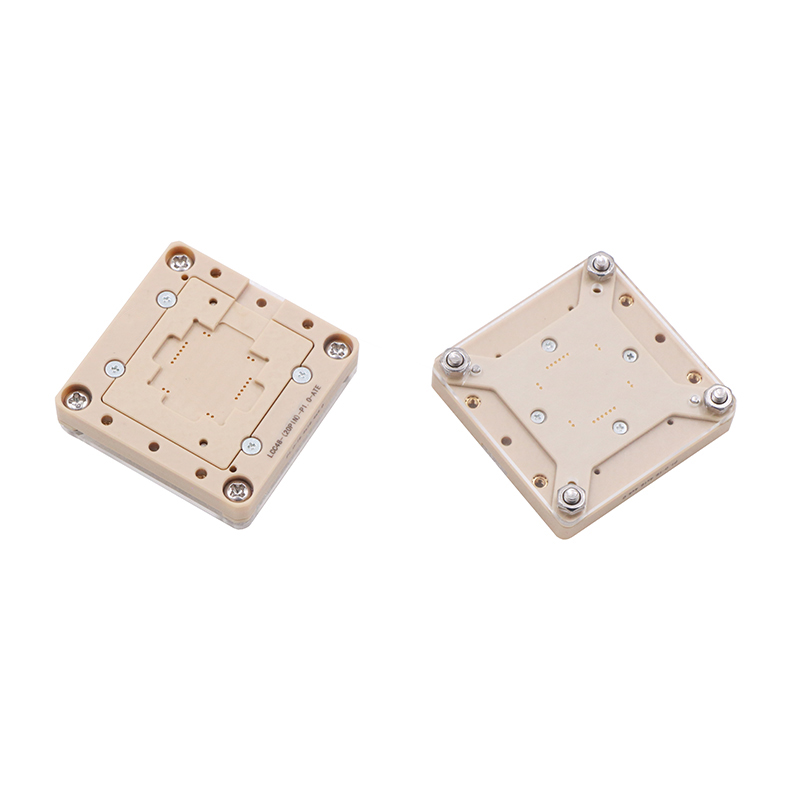

2. 耐高温FT测试座

支持双通道测试(如同时验证SiC模块的开关特性与热阻),接触寿命>50万次[citation:用户历史案例]。

采用低介电常数材料(如LCP),寄生电感<1nH,满足GaN器件10MHz以上开关频率的测试需求。

3. IC老化座与烧录座集成方案

IC老化座支持多芯片并行老化(如48颗GaN芯片同时测试),温度均匀性±1℃[citation:用户历史案例]。

IC烧录座集成JTAG边界扫描功能,可在FT阶段直接修复存储器缺陷,提升良率5%以上。

五、未来趋势:智能化与国产化

1. AI驱动的测试优化

通过机器学习分析CP/FT测试数据,预测晶圆制造缺陷(如边缘区域裸片的高失效率),动态调整测试策略。

2. 国产设备替代

谷易电子等厂商正推动晶圆测试探针卡、IC/芯片测试座scket的国产化,成本较进口产品降低30%,市场份额逐步提升,

CP与FT测试是第三代半导体量产化的关键保障,两者的协同优化可显著提升SiC/GaN芯片的良率与可靠性。谷易电子通过定制化IC/芯片测试座与智能化方案,为行业提供了高性价比的国产替代选择,助力中国半导体产业突破技术壁垒。未来,随着8英寸SiC晶圆的普及与测试设备智能化,第三代半导体的应用边界将进一步扩展。

在线咨询

在线咨询

扫一扫关注官方微信

13823541376

13823541376