服务热线 13823541376

深圳市谷易电子有限公司

联系电话:13823541376

联系人:兰小姐

邮箱:sales@goodesocket.com

主营产品:定制测试座、老化测试座、弹片微针模组、memory测试座、测试夹具、BGA老化测试、QFN老化测试、Flash闪存测试、编程烧录座

发表时间:2025-05-15 15:24:14浏览量:744【小中大】

芯片复杂度与集成度的指数级增长,系统级测试(SLT)已成为确保芯片功能、性能与可靠性的关键环节。尤其在5G、AI与车规级芯片领域,SLT不仅需要覆盖功能验证、高速接口测试与DDR内存性能评估,还需通过ESD、HTOL、HAST等严苛可靠性测试筛选潜在缺陷。本文从测试要求、技术特点及关键设备角度,结合谷易电子的芯片测试座、老化座与DDR夹具解决方案,深度解析SLT测试的全链路创新。

一、SLT功能测试:真实场景下的芯片“体检”

核心要求与技术特点

功能测试是SLT的基石,旨在验证芯片在真实应用环境中的逻辑正确性,其核心挑战包括:

全功能覆盖:需模拟操作系统启动、多任务并发等复杂场景,确保IP模块间交互无异常。

信号完整性保障:测试板需集成PMIC、RAM、PCIe外设等真实硬件,避免信号衰减或时序偏移。

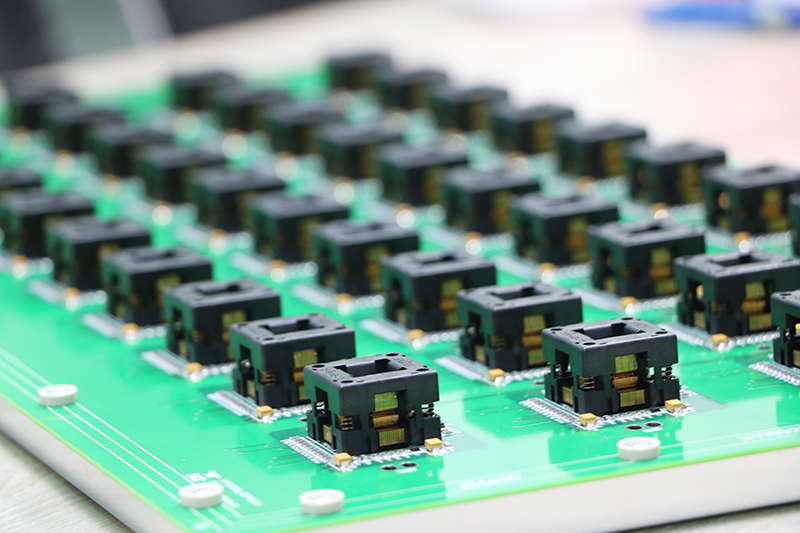

测试效率优化:SLT测试时间通常长达数十分钟,需通过并行测试架构(如16工位)降低单颗成本。

谷易电子的关键应用

针对功能测试需求,谷易电子推出高密度芯片测试座与智能转接座:

多封装兼容设计:适配LGA、BGA、QFN等封装,探针间距低至0.35mm,支持10万次插拔寿命。

板载信号调理模块:集成阻抗匹配与滤波电路,降低高频信号反射,提升测试稳定性。

二、高速接口与DDR测试:性能极限的“压力测试”

高速接口测试

面向PCIe 5.0、USB4等接口,测试需满足:

40GHz以上带宽:验证信号眼图、抖动容限及误码率(BER≤1E-12)。

温度动态补偿:在-55℃~125℃范围内校准时序偏差,确保车规芯片的宽温域适应性。

DDR内存测试

DDR4/5测试的核心参数包括:

时序校准:通过Fly-by拓扑优化时钟偏移,确保tCL、tRCD等参数达标。

功耗与散热评估:在1.1V超低电压下监测动态功耗,结合热电偶实时反馈结温。

谷易电子的创新方案

DDR内存颗粒测试夹具:支持双通道DDR5-6400,集成IBIS模型仿真功能,可预判信号完整性风险。

高速探针阵列:采用镀金铍铜材质,接触电阻<10mΩ,适配0.5mm超细间距BGA封装。

三、可靠性测试:芯片“耐久力”的终极考验

核心测试项与标准要求

1. ESD测试

HBM模型:要求2kV接触放电,峰值电流1.2~1.48A,确保I/O引脚无漏电(<1μA)。

CDM模型:模拟封装带电放电,测试电压500V,电流峰值>10A,筛选电荷泄放失效。

2. Latch-up测试

通过注入1.5倍VDD电流,验证闩锁效应抑制能力,确保失效电流>200mA。

3.HTOL/LTOL测试

HTOL:125℃下动态运行1000小时,筛选电迁移与氧化层破裂缺陷。

LTOL:-40℃低温环境测试,验证金属界面热应力耐受性。

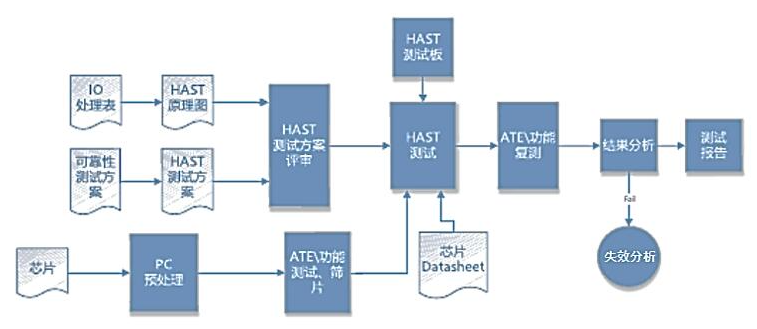

4. TCT/HAST测试

TCT:-55℃~125℃循环1000次,检测分层与焊点疲劳。

HAST:130℃、85%湿度下加压96小时,评估封装密封性与离子迁移风险。

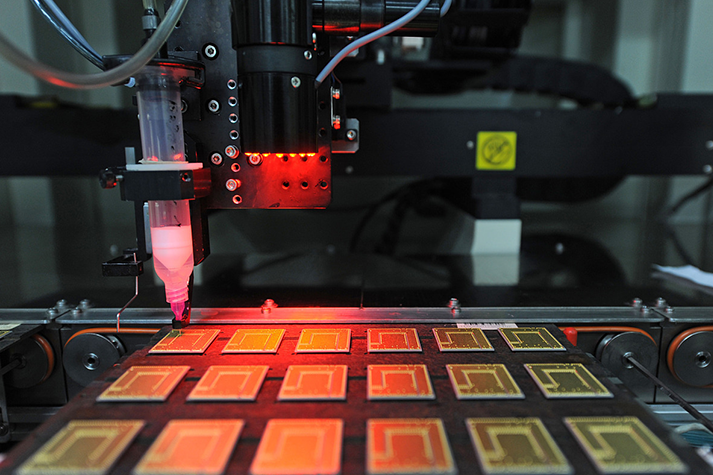

谷易电子的可靠性测试设备

宽温域芯片老化座:支持-65℃~150℃温度冲击,内置热电偶实时监测结温漂移。

抗ESD测试座:采用碳纤维基板(CTE匹配芯片封装),避免热变形导致接触失效。

四、SLT测试的技术挑战与协同创新

测试效率与成本平衡

并行测试架构:通过16工位同步测试,将吞吐量提升300%,单位成本降低40%。

AI驱动的测试优化:利用机器学习分析HTOL数据,预测失效模式并动态调整测试参数。

国产化突破

谷易电子芯片测试座通过模块化设计与高寿命探针(寿命达50万次),实现芯片测试座成本仅为进口方案的1/3,并支持DDR5、PCIe 6.0等前沿接口适配。

五、未来趋势:智能化与三维集成

AIoT芯片测试:集成边缘计算单元,实现测试数据的实时分析与远程诊断。

3D IC测试:开发垂直探针阵列与TSV通孔检测技术,适配Chiplet异构集成需求。

在线咨询

在线咨询

扫一扫关注官方微信

13823541376

13823541376