服务热线 13823541376

深圳市谷易电子有限公司

联系电话:13823541376

联系人:兰小姐

邮箱:sales@goodesocket.com

主营产品:定制测试座、老化测试座、弹片微针模组、memory测试座、测试夹具、BGA老化测试、QFN老化测试、Flash闪存测试、编程烧录座

发表时间:2025-07-21 14:41:00浏览量:551【小中大】

一、SPM封装测试技术与关键应用

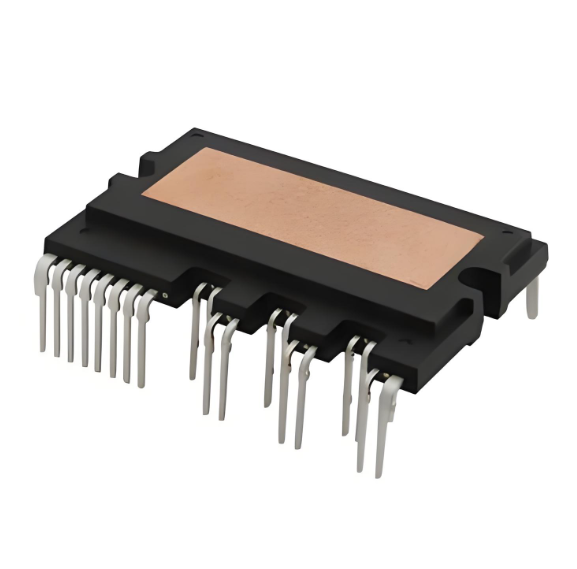

1. 封装特性与测试需求

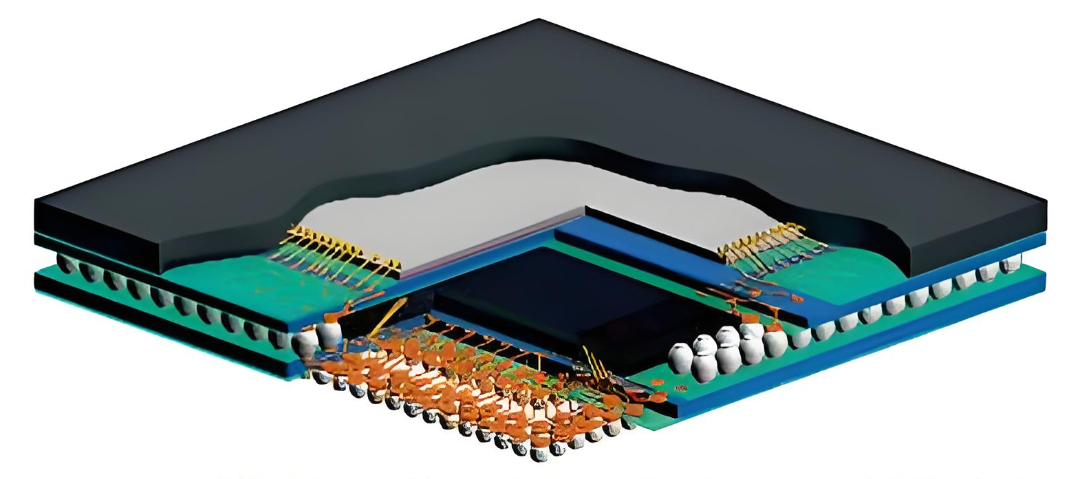

智能功率模块(SPM)作为IPM的升级形态,采用DBC基板、粗铝线互联及塑封工艺,集成IGBT、FRD等功率器件与控制电路。其测试需关注以下核心项:

电气参数:导通电阻(Rdson)、击穿电压(BVdss)、漏电流(Igss),需采用脉冲法避免自热效应,测试设备需支持500A大电流。

热性能:热阻(RθJA)、结温(TJ)及散热效率,遵循JEDEC JESD51-1标准,通过热敏参数(TSP)法测量。

机械可靠性:塑封体抗开裂能力、引脚共面度(公差<0.1mm),需通过温度循环(-55℃~125℃)和振动测试(20Grms)验证。

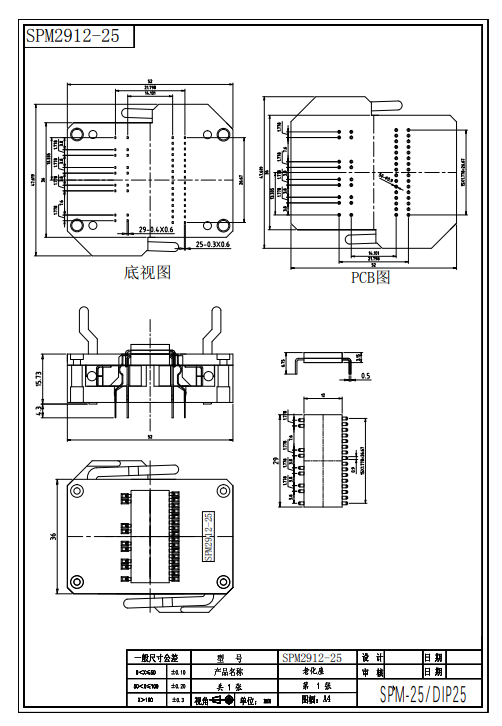

2. 谷易SPM测试座解决方案

谷易电子针对SPM开发的测试座采用高精度探针(间距0.35mm)和镀金铍铜材质,接触电阻<10mΩ,支持10万次插拔寿命。其板载信号调理模块集成阻抗匹配电路,可降低高频信号反射(如10MHz开关频率下寄生电感<1nH),满足SiC模块的动态测试需求。典型应用包括:

汽车电子:

车载逆变器IGBT模块的三温测试(-40℃/25℃/175℃),导通电阻偏差需<5%。

工业控制:风电变流器SPM的高温开关损耗测试(150℃下损耗增加≤10%),结合液冷散热模块实现结温控制≤150℃。

3. 测试标准与方法

电气测试:使用高精度SMU(源测量单元)配合ATE设备,测试精度达±0.1%。

热测试:红外热成像仪监测芯片表面温度分布,结合热电偶实时反馈结温,确保符合JEDEC标准。

机械测试:依据IPC-9701标准,静压测试(50-200kg压力)下形变需≤5%封装高度,阻抗波动≤15%。

二、SOM封装测试技术与关键应用

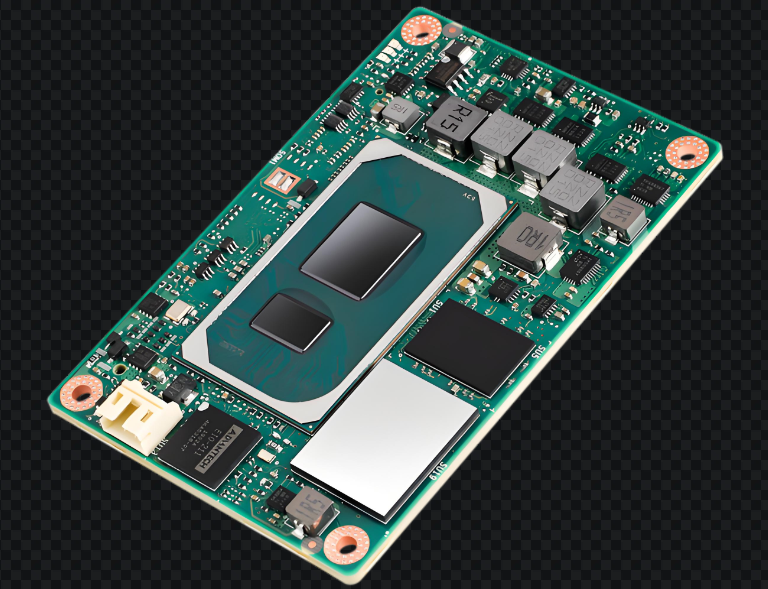

1. 封装特性与测试需求

系统级模块(SOM)集成处理器、内存、接口控制器等,需验证复杂功能与信号完整性。测试项包括:

功能验证:

操作系统启动、多任务并发处理,需模拟真实应用场景(如工业物联网网关的边缘计算)。

高速接口:PCIe 5.0(40GHz带宽)、USB4(40Gbps速率)的眼图余量(≥0.3UI)、误码率(BER≤1E-12)。

电源管理:动态功耗(如1.1V超低电压下的电流波动)、PMIC输出稳定性,需支持多通道电流(单Pin 1.5A)监测。

2. 谷易SOM测试座解决方案

谷易高密度测试座适配LGA、BGA等封装,探针间距低至0.35mm,支持DDR5-6400双通道测试,集成IBIS模型仿真功能预判信号完整性风险。其板载阻抗匹配电路(±3%精度)可消除PCIe 5.0信号反射,眼图测试余量达0.35UI。典型应用包括:

边缘计算:工业网关SOM的多协议(Modbus/OPC UA)并发测试,单日筛选20万颗,不良率<10ppm。

医疗设备:脑机接口芯片的γ波段(25-100Hz)信号完整性测试,接触电阻<15mΩ,满足ISO 13485医疗合规性。

3. 测试标准与方法

功能测试:基于ATE的无代码开发平台(如ATECLOUD),支持多参数并行测试,测试时间缩短30%。

信号完整性:矢量网络分析仪(VNA)测量S参数(插入损耗<2dB),结合TDR验证阻抗匹配(50Ω±5%)。

环境可靠性:HAST测试(130℃/85%RH/96小时)评估封装密封性,满足JEDEC JESD22-A110标准。

三、POP封装测试技术与关键应用

1. 封装特性与测试需求

堆叠封装(POP)通过锡球或TSV实现逻辑芯片与存储芯片垂直互联,测试挑战包括:

机械稳定性:堆叠后翘曲控制(≤50μm)、焊球剪切强度(≥50gf),需通过激光扫描和静压测试(50-100kg)验证。

信号完整性:高速接口(如HBM带宽>2TB/s)的时序偏差(温度补偿范围-55℃~125℃)、眼图余量(≥0.3UI)。

热管理:双面散热设计下的结温分布(温差≤5℃),需红外热成像与热电偶同步监测。

2. 谷易POP测试座解决方案

谷易电子的POP测试座采用高精度对位机构(±5μm)和多轴振动测试(20Grms),适配0.4mm焊球间距。其液冷散热模块可实现3kW/cm²散热功率,确保HBM在1.2-1.48A峰值电流下结温≤150℃。典型应用包括:

消费电子:智能手机AP+DRAM堆叠模块的高速数据传输测试(如LPDDR5X 6400Mbps速率),误码率≤1E-12。

数据中心:GPU+HBM的PCIe 6.0接口测试(112G PAM4信号),眼图余量≥0.35UI,阻抗匹配±3%。

3. 测试标准与方法

机械测试:依据JEDEC JESD22-B117和IPC-9701,静压测试保压1-5分钟,允许形变≤5%封装高度。

热测试:温度循环(-65℃~150℃)1000次,监测焊点疲劳裂纹扩展,符合JEDEC JESD22-A104标准。

电气测试:自动测试机(ATE)配合高速探针阵列,支持多通道并行测试(如16工位),效率提升80%。

四、谷易电子IC测试座技术优势与行业价值

1. 高可靠性设计:探针寿命达50万次,接触电阻<10mΩ,满足车规级芯片(AEC-Q100)的严苛要求。

2. 成本优化:模块化设计使测试座成本仅为进口方案的1/3,适配国产半导体产业链降本需求。

3. 前沿技术适配:支持DDR5、PCIe 6.0等下一代接口,帮助客户快速验证3D封装与Chiplet技术。

通过上述技术解析与应用案例可见,谷易电子IC测试座方案为SPM、SOM、POP封装提供了从研发到量产的全流程可靠性保障,推动国产半导体测试技术迈向国际前沿。

在线咨询

在线咨询

扫一扫关注官方微信

13823541376

13823541376