服务热线 13823541376

深圳市谷易电子有限公司

联系电话:13823541376

联系人:兰小姐

邮箱:sales@goodesocket.com

主营产品:定制测试座、老化测试座、弹片微针模组、memory测试座、测试夹具、BGA老化测试、QFN老化测试、Flash闪存测试、编程烧录座

发表时间:2025-08-20 10:58:12浏览量:591【小中大】

一、核心技术架构与工作原理

1. 高速计算芯片的技术突破

AI与机器人领域的高速计算芯片(如GPU/TPU/ASIC)采用异构计算架构实现性能跃升:

并行计算单元:NVIDIA H100的SXM5架构集成912亿晶体管,通过5120个CUDA核心与60个Tensor核心实现FP8精度下600 TFLOPS算力。

动态功耗管理:AMD MI300X的Infinity Cache技术结合DVFS(动态电压频率调节),在ResNet-50训练中功耗降低23%。

先进封装技术:台积电CoWoS封装通过硅中介层(Interposer)实现芯片间TSV(硅通孔)互联,带宽达900GB/s,较传统封装提升3倍。

2. 高速读写芯片的性能革新 HBM(高带宽内存)与UFS控制器通过三维堆叠与协议优化突破存储瓶颈:

HBM3的TSV技术:SK海力士HBM3E采用12层堆叠,通过2000+ TSV实现3.35TB/s带宽,较GDDR6X提升4倍。

UFS 4.0协议:支持HS-Gear4接口(11.6Gbps),配合Write Turbo技术实现1200MB/s随机写入,较UFS 3.1提升50%。

3D NAND堆叠:三星238层QLC NAND通过电荷陷阱技术将P/E次数提升至10万次,满足工业级耐久性需求。

二、关键应用场景与技术适配

1. 高速计算芯片的典型应用

大模型训练集群:Google TPU v5 Pod采用128颗芯片互联,在GPT-4训练中实现90%以上的算力利用率。

自动驾驶域控制器:特斯拉HW4.0的D1芯片通过36颗ASIC实现254TOPS/W能效比,支持实时多传感器融合。

工业机器人控制:发那科R-30iB Mate Plus系统搭载AI芯片,实现0.1ms级运动轨迹预测与碰撞规避。

2. 高速读写芯片的场景落地

边缘AI推理:美光HBM2E在智能摄像头中实现1080P@60fps视频分析,功耗较传统方案降低40%。

车载信息娱乐系统:西部数据iNAND 9030采用UFS 3.1协议,支持8K视频解码与多任务并发处理。

医疗影像处理:Kioxia CM7系列NVMe SSD通过PCIe 5.0接口实现8GB/s连续读取,加速CT图像重建。

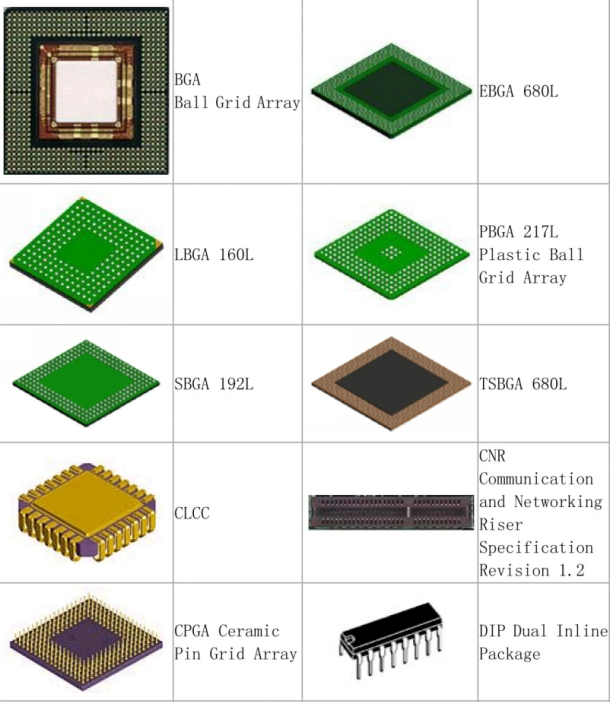

三、先进封装技术与测试挑战

1. 高速计算芯片的封装创新

CoWoS封装流程:

(1)硅中介层制备:通过TSV电镀与微凸块(μBumps)形成垂直互联。

(2)芯片集成:GPU/DPU/缓存芯片通过倒装焊(Flip Chip)与中介层键合,实现<1μm对准精度。

(3)散热设计:台积电3D Fabric技术结合铜柱凸块(Cu Pillar),热阻降低至1.2K/W。

2. 高速读写芯片的封装演进

HBM的3D堆叠:

采用2.5D封装将DRAM die与逻辑芯片集成于同一基板,TSV密度达10^6/cm²。UFS控制器封装:三星Exynos Modem 5300采用PoP(Package-on-Package)技术,厚度压缩至1.2mm。

封装测试的核心难点

电气可靠性:CoWoS中介层的TSV空洞率需<5%,通过X射线显微镜(XRM)检测。

热管理验证:HBM3在150℃高温下需保持<10%的信号完整性衰减,采用红外热像仪监测。

机械应力测试:UFS芯片需通过IPC-9701标准的1000次温度循环(-40℃~125℃),确保焊点无开裂。

四、全生命周期测试体系与标准

1. 高速计算芯片的测试框架

2. 高速读写芯片的测试体系

五、谷易电子芯片测试座解决方案的关键作用

1. 芯片测试座的技术突破

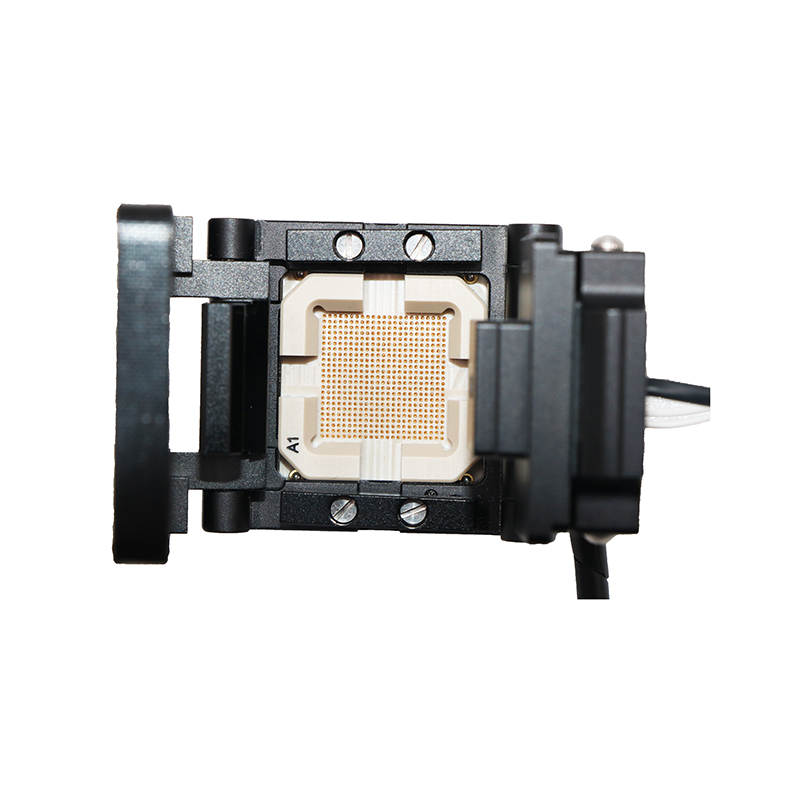

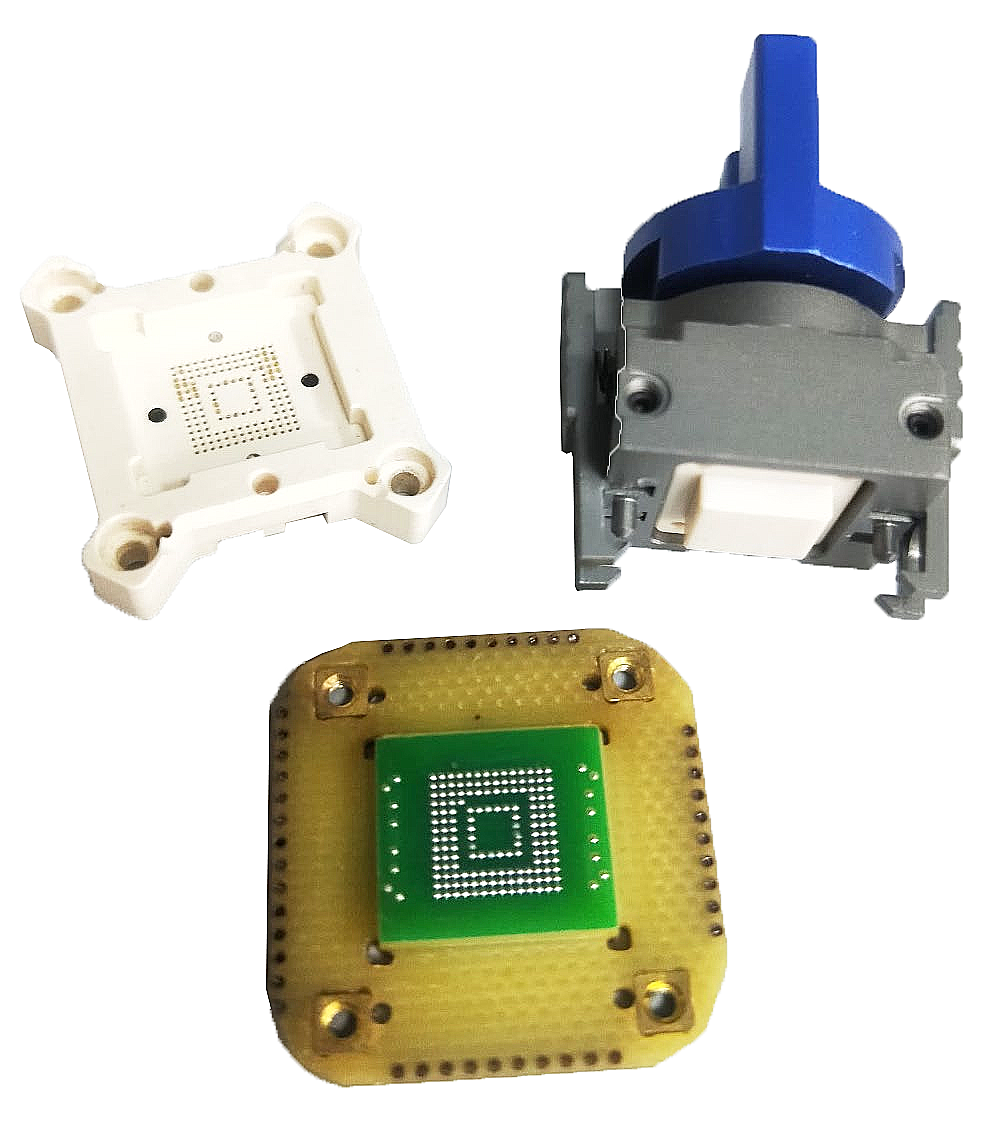

高精度接触设计:

采用全镀硬金铍铜探针,接触电阻<50mΩ,支持0.35mm间距焊球检测。

专利旋钮机构解决0.4mm间距桥连问题,良率提升至99.97%,适配CoWoS微凸块测试。

高频信号支持: - 56GHz同轴探针设计,寄生电感<0.1nH,满足PCIe 5.0(32GT/s)与CXL 2.0协议测试。

2. 老化座的可靠性保障

宽温域控制:

支持-55℃~175℃老化测试,温度均匀性±1℃,满足车规级芯片三温验证。

集成热电偶与电压监控模块,实时追踪结温与功耗曲线,支持10万小时以上老化。

多通道并行测试:单块老化板支持96颗eMMC或80颗UFS芯片同时测试,通过液冷模块实现散热效率提升30%。

3. 烧录座的智能化赋能

高速编程能力:支持10Gbps速率下的并行编程,JTAG边界扫描覆盖率≥95%,可修复5%的存储器缺陷。

自动化适配:兼容SMEMA标准产线,实现每秒2次以上的上下料操作,支持AI驱动的自适应校准,误判率<0.01%。

六、行业标准与未来趋势

1. 核心技术标准

高速计算芯片:MLPerf推理v3.0要求ResNet-50延迟<1ms,OCP 48V电源规范定义能效比≥3 TOPS/W。

高速读写芯片:JEDEC JESD235B定义HBM3E的12层TSV堆叠标准,UFS协会发布UFS 4.0白皮书规范1200MB/s随机写入。

2. 技术演进方向

高速计算芯片:

存算一体架构:三星HBM-PIM将计算单元集成于存储芯片,带宽利用率提升80%。

光子计算:Lightmatter Envo采用硅光技术,功耗降低至传统芯片的1/10。

高速读写芯片:MRAM技术:Everspin STT-MRAM实现10^15次写入寿命,替代部分NOR Flash应用。

CXL协议:美光CXL 3.0 SSD通过内存池化技术,延迟降低至5μs。

3. 测试技术革新

AI驱动测试:谷易的机器学习模型可动态生成测试用例,缺陷检出率提升30%。

数字孪生验证:武汉精测的虚拟仿真系统可提前预测芯片在极端工况下的性能表现。

在线咨询

在线咨询

扫一扫关注官方微信

13823541376

13823541376