服务热线 13823541376

深圳市谷易电子有限公司

联系电话:13823541376

联系人:兰小姐

邮箱:sales@goodesocket.com

主营产品:定制测试座、老化测试座、弹片微针模组、memory测试座、测试夹具、BGA老化测试、QFN老化测试、Flash闪存测试、编程烧录座

发表时间:2025-11-03 09:43:06浏览量:709【小中大】

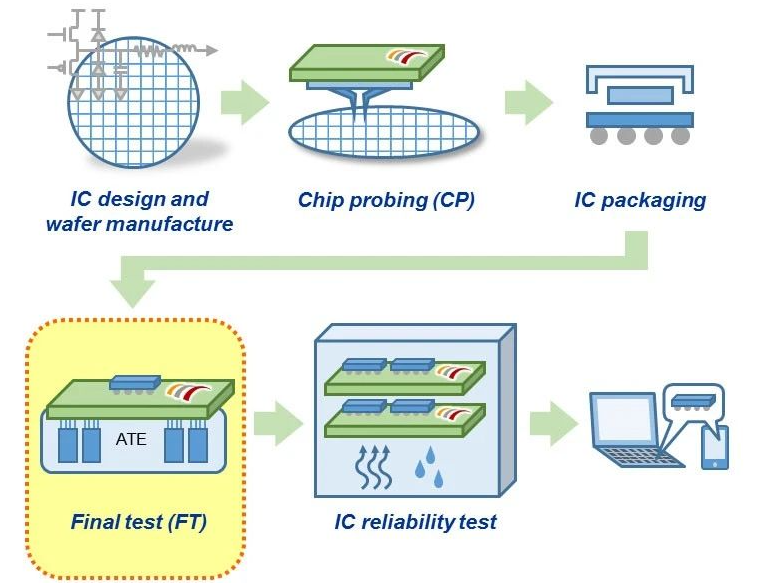

CP 测试(Chip Probe Test)针对未切割的晶圆,通过 ATE 设备输出测试信号,经芯片测试座的探针接触晶圆上的 “测试焊盘”(Pad),采集芯片的电压、电流、时序等电性参数,判断芯片是否存在短路、开路、功能失效等早期缺陷。测试完成后,通过标记系统标注不良芯片,避免后续封装环节的无效成本。

测试时机早:在晶圆切割前完成筛选,剔除 80% 以上的早期不良品,降低封装成本(封装一颗不良芯片的成本约为测试成本的 5-8 倍);

精度要求高:晶圆焊盘尺寸极小(最小仅 20μm),且相邻焊盘间距窄(≤50μm),需芯片测试座实现 “微米级精准接触”;

环境可控性强:需在洁净室(Class 100)内进行,芯片测试座需具备抗污染、低磨损特性,避免损伤晶圆表面。

逻辑芯片:CPU、GPU 晶圆的核心算力单元功能测试,需验证时钟频率、指令执行效率;

存储芯片:DDR5、NAND 闪存晶圆的存储单元读写速度、数据保持能力测试;

功率芯片:IGBT、SiC 晶圆的导通压降、击穿电压等电性参数筛查,避免封装后高温失效。

针对 CP 测试的“微间距、高精度” 需求,谷易采用微针阵列结构设计:

探针直径最小达 30μm,针尖采用铑钌合金镀层,硬度达 HV500 以上,单次晶圆测试的探针磨损率<0.1%,可连续测试 5 万片晶圆无需更换;

芯片测试座底座采用陶瓷材质(热膨胀系数与硅晶圆接近,仅 3.2ppm/℃),避免温度变化导致的探针偏移,接触对准精度达 ±2μm;

适配 “晶圆尺寸兼容” 设计,支持 8 英寸、12 英寸晶圆通用,更换晶圆型号时无需更换芯片测试座主体,仅需更换探针模组,切换时间缩短至 30 分钟以内。

FT 测试(Final Test)针对已完成封装的芯片(如 DIP、SOP、QFN、BGA 封装),将芯片插入芯片测试座,通过 ATE 设备模拟芯片实际工作场景(如不同电压、温度、负载条件),全面验证芯片的功能完整性、性能稳定性及可靠性,最终筛选出符合规格的成品芯片。

测试场景全:覆盖 “静态参数(如漏电流)、动态功能(如信号时序)、可靠性(如温循稳定性)” 三类测试,模拟芯片实际应用环境;

封装兼容性广:需适配十余种封装类型,尤其是细间距封装(如 0.4mm 间距 BGA)、异形封装(如 LGA-1700),对芯片测试座的结构设计要求极高;

效率优先:成品测试需满足批量生产需求,单颗芯片测试时间通常要求<10 秒,需芯片测试座支持 “快速插拔 + 稳定接触”。

车规芯片:MCU、功率管理芯片的 “高温老化测试”(125℃下连续工作 1000 小时),验证极端环境下的可靠性;

消费电子芯片:手机 SoC 的 “射频性能测试”,需芯片测试座支持 5G 毫米波信号传输,衰减<1.5dB;

工业芯片:PLC 控制芯片的 “抗干扰测试”,模拟强电磁环境下的信号稳定性,芯片测试座需具备电磁屏蔽能力(屏蔽效能≥40dB)。

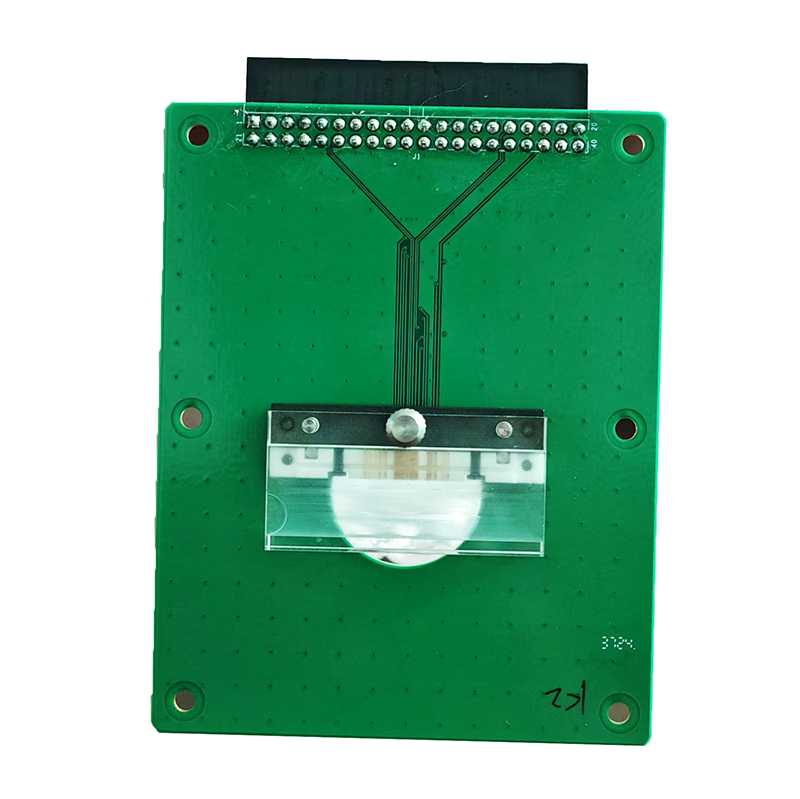

针对 FT 测试的“多封装、高可靠” 需求,谷易推出模块化芯片测试座体系:

接触结构定制:

针对 BGA 封装:采用 “球型接触端子”,端子顶部为弧形设计,与 BGA 焊球的接触面积提升 30%,避免焊球压伤,不良接触率<0.01%;

针对 QFN 封装:采用 “弹性爪式端子”,端子具备 0.2mm 的弹性行程,适配封装尺寸偏差(±0.1mm),兼容不同厂商的封装公差;

极端环境适配:

高温芯片测试座:壳体采用 PEEK 耐高温材料(耐温 260℃),端子采用铍铜合金(弹性系数稳定),在 150℃下连续测试 500 小时,接触阻抗变化<3mΩ;

防潮测试座:具备 IP65 防护等级,在 85% 湿度、85℃环境下(HAST 测试条件),测试座内部无凝露,确保测试稳定性;

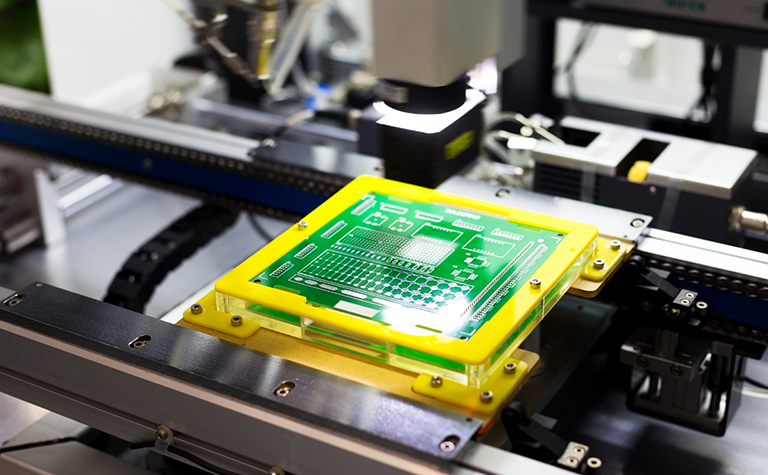

自动化兼容:

支持 “机械手自动插拔”,芯片测试座定位精度达 ±0.05mm,适配 ATE 设备的多工位并行测试(如 8 工位同步测试),单日测试产能提升至 5 万颗以上。

测试效率高:替代手动测试,单台 ATE 设备的测试效率是手动测试的 50-100 倍,适配大规模量产需求;

测试精度准:ATE 设备的信号分辨率达 μV 级(电压)、nA 级(电流),时序精度达 ps 级,需测试座具备 “低信号损耗” 特性;

可扩展性强:支持通过更换芯片测试座、升级测试软件,适配不同型号、不同类型的芯片(如从逻辑芯片切换到模拟芯片)。

批量量产检测:消费电子芯片(如快充芯片)的大规模 FT 测试,单台 ATE 设备搭配谷易芯片测试座,可实现每秒 2 颗的测试速度;

高端芯片研发:车规 MCU 的 “定制化功能测试”,通过 ATE 软件编写专属测试程序,配合封装芯片测试座的稳定接触,验证芯片的特殊功能(如安全加密模块);

可靠性验:工业芯片的 “长期老化测试”,ATE 设备与芯片测试座配合,连续 72 小时监测芯片参数变化,筛选出 “早期失效品”。

谷易针对 ATE 设备的 “高兼容性、低损耗” 需求,打造 “ATE - 测试座” 协同方案:

信号完整性优化:芯片测试座内部采用 “阻抗匹配设计”(特性阻抗 50Ω/75Ω 可选),信号传输损耗<0.5dB@10GHz,适配 ATE 设备的高频测试需求(如 5G 芯片的毫米波测试);

多协议兼容:支持 SPI、I2C、PCIe、USB4.0 等主流芯片通信协议,芯片测试座无需硬件改造,仅通过 ATE 软件配置即可切换协议类型;

数据反馈实时性:测试座内置 “接触状态监测模块”,可实时反馈探针接触阻抗(精度 ±1mΩ),若出现接触不良,立即触发 ATE 设备报警,避免批量误判,不良品漏检率降至 0.001% 以下。

谷易电子首创 “自适应接触系统”,通过三类核心结构覆盖全场景:

微针结构:适配 CP 测试的微间距焊盘,针尖曲率半径精准控制在 5-10μm,确保 “小面积、高压力” 接触,避免焊盘损伤;

弹性端子结构:适配 FT 测试的成品芯片,端子弹性系数可根据芯片引脚材质(如铜、金、锡)定制,接触压力误差<5g;

磁吸定位结构:针对 BGA、LGA 等无引脚封装,通过磁吸定位实现 “零偏移” 接触,定位精度达 ±0.02mm。

接触材料:采用 “铍铜 + 镀金 / 铑钌合金” 复合镀层,硬度达 HV450,耐插拔次数超 10 万次,腐蚀 resistance(盐雾测试)达 96 小时无锈蚀;

壳体材料:高温场景采用 PEEK(耐温 260℃),高频场景采用 PTFE(介电常数 2.1),潮湿场景采用玻纤增强 PPA(吸水率<0.1%),确保不同环境下的结构稳定性。

车规芯片测试:为某头部车企提供的 SiC 功率芯片 FT 测试座,支持 175℃高温老化测试,连续测试 1000 小时后,接触阻抗变化<2mΩ,芯片良率从 82% 提升至 95%;

消费电子芯片测试:为 TWS 耳机芯片提供的 CP 测试座,适配 0.3mm 间距晶圆,单次测试晶圆数量从 20 颗 / 小时提升至 50 颗 / 小时,测试成本降低 35%;

工业芯片测试:为 PLC 芯片提供的 ATE 兼容测试座,支持 - 40℃~125℃宽温测试,抗电磁干扰能力达 EMC Class B 标准,不良品检出率提升至 99.99%。

在芯片向 “微型化、高频化、高可靠性” 发展的趋势下,CP/FT/ATE 测试已从 “质量把关” 升级为 “良率提升核心手段”,而芯片测试座作为连接芯片与测试设备的 “关键节点”,其技术水平直接决定测试体系的效能。谷易电子通过接触技术创新、材料升级与场景化设计,不仅解决了 “微间距适配、极端环境稳定、多协议兼容” 等行业痛点,更推动芯片测试从 “被动检测” 向 “主动优化良率” 转型,为车规、消费、工业等领域的芯片量产提供了核心支撑,成为芯片测试产业链中不可或缺的技术载体。

在线咨询

在线咨询

扫一扫关注官方微信

13823541376

13823541376