服务热线 13823541376

深圳市谷易电子有限公司

联系电话:13823541376

联系人:兰小姐

邮箱:sales@goodesocket.com

主营产品:定制测试座、老化测试座、弹片微针模组、memory测试座、测试夹具、BGA老化测试、QFN老化测试、Flash闪存测试、编程烧录座

发表时间:2026-03-11 10:21:05浏览量:104【小中大】

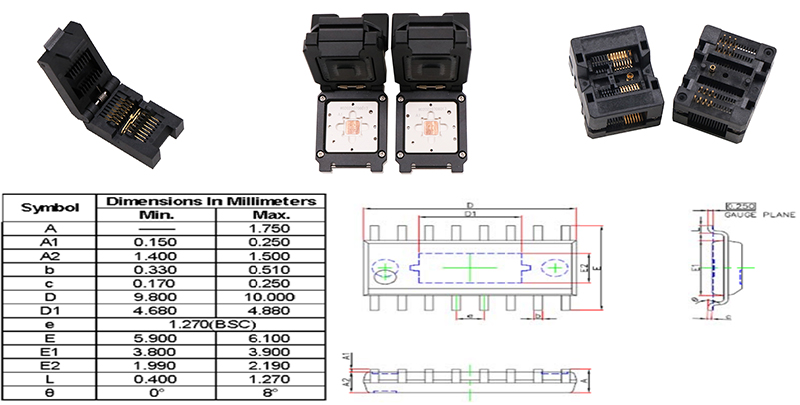

芯片测试座(socket)作为芯片与测试设备之间的核心连接桥梁,承担着信号传输、环境模拟、精准对接的关键职责,其设计合理性直接决定芯片测试的精度、效率与可靠性。接地设计作为芯片测试座的核心技术要点之一,是保障测试稳定性、规避干扰、保护芯片与设备的关键环节。

一、芯片测试座中接地的定义

芯片测试座中的接地,本质是在测试座结构中构建低阻抗的电流回流通道,通过专用接地探针、金属构件(外框、固持座)等结构,将测试过程中产生的杂散电流、静电电荷、干扰信号,以及芯片与测试设备的多余电位,引导至大地或测试系统的参考地极,形成“测试座-接地结构-大地”的完整导通回路。

与普通电路接地不同,芯片测试座的接地需兼顾“精准传导”与“隔离防护”双重需求,既要实现干扰信号的快速导泄,又要避免接地结构与信号探针之间产生串扰,保障测试信号的纯净度。结合谷易电子共地型芯片测试座的专利设计(CN 117434304 A),其接地结构采用“金属外框+金属固持座+接地弹簧探针”的共地架构,使三者电性耦接形成统一接地网络,实现全域低阻抗接地,这也是行业内高端测试座的主流接地设计思路。

二、芯片测试座中接地的核心作用(结合谷易电子案例应用)

谷易电子作为IC测试座领域的专业解决方案提供商,深耕车规、高频、精密芯片测试场景,其测试座产品凭借科学的接地设计,在BMS MCU、AFE、5G射频芯片等测试场景中实现成熟应用,其接地设计的核心作用可归纳为以下4点,每一点均结合谷易电子实际应用案例展开说明。

(一)抑制电磁干扰,保障测试信号纯净度

芯片测试过程中,尤其是高频芯片(如5G射频芯片)、车规芯片的测试,测试座与芯片、测试设备之间会产生电磁辐射干扰,同时信号探针之间易出现串扰,导致测试信号失真,影响测试数据的准确性。接地设计通过构建屏蔽与导泄回路,可有效抑制这类干扰。

谷易电子在高频芯片测试座中采用“多层隔离+精准接地”的复合结构,内置多路径接地网络,将屏蔽套管、合金外壳与测试系统地极形成低阻抗连接,接地电阻稳定在10mΩ以内,可快速将干扰信号导地,实现高频信号0失真传输。例如,某5G射频芯片厂商采用谷易QFN封装测试座,通过其优化的接地屏蔽设计,有效解决了高频信号串扰问题,单日完成20万颗芯片筛选,测试不良率控制在10ppm以内,大幅提升了测试效率与精准度。此外,谷易在车规MCU芯片测试座设计中,通过“电源区域与信号区域隔离+接地屏蔽层”的设计,将电源针脚集中布置并增设接地屏蔽,有效避免了电源噪声对信号pin脚测试的干扰,适配新能源汽车电池芯片的严苛测试需求。

(二)导泄静电电荷,保护芯片与测试设备安全

芯片(尤其是精密半导体芯片)对静电极为敏感,测试过程中,芯片与测试座探针的接触、分离,以及操作环境的摩擦,都会产生静电电荷。若静电无法及时导泄,会积聚在芯片表面或测试座内部,轻则导致测试数据漂移,重则击穿芯片内部电路,造成芯片损坏;同时,静电积累还可能影响测试设备的正常运行,引发设备故障。

谷易电子在测试座设计中,将接地结构与防静电设计深度融合,其共地型测试座的接地弹簧探针一端与芯片承载区域接触,另一端连接测试系统地极,形成“静电吸附-传导-导泄”的闭环体系。结合谷易新能源汽车电池芯片测试座的应用案例,该系列测试座适配BMS MCU、AFE等敏感芯片,通过接地弹簧探针与金属固持座、外框的共地架构,可快速导泄±15kV的静电,静电消散时间≤1ns,符合ANSI/ESD S20.20防静电标准,有效避免了静电对电池芯片的损伤,保障了测试过程中芯片与测试设备的安全。

(三)稳定测试电位,提升测试数据的一致性

芯片测试的核心需求是获取精准、一致的测试数据,而测试座与芯片、测试设备之间的电位不稳定,会导致测试数据漂移,出现“同批次芯片测试结果差异过大”的问题。接地设计可构建统一的电位参考基准,使芯片、测试座、测试设备处于同一电位水平,避免电位差带来的测试误差。

谷易电子在测试座接地设计中,严格控制接地回路的阻抗,通过优化接地探针的材质(采用黄铜镀金处理,降低接触电阻)与结构(紧配合固持于金属固持座,确保导通稳定),使接地回路的导通电阻≤0.1Ω,保障电位传输的稳定性。例如,在车规芯片批量测试场景中,谷易测试座通过稳定的接地设计,将测试数据的漂移率控制在0.05%以下,确保同批次芯片的测试数据一致性,为芯片筛选提供了可靠的依据。同时,其金属固持座采用双金属板结构,兼顾接地稳定性与结构强度,在高低温循环测试中,接地性能无明显变化,进一步保障了测试数据的稳定性。

(四)规避漏电风险,保障操作人员安全

芯片测试过程中,测试设备会向芯片施加一定的测试电压,若测试座存在漏电情况,可能导致操作人员触电,同时也会损坏测试设备与芯片。接地设计可作为漏电保护的重要环节,将测试座与测试设备的漏电流快速导泄至大地,避免漏电流积聚,保障操作人员的人身安全。

谷易电子在测试座设计中,将金属外框、接地探针与测试系统的保护地(PE)可靠连接,形成完整的漏电导泄回路。其共地型测试座的金属外框底缘设有环形凹槽,金属固持座固定于凹槽内,接地弹簧探针的一端突伸出外框底缘,与测试设备的接地端精准对接,确保漏电流可快速导地。在新能源汽车电池芯片测试等高压测试场景中,这种接地设计可有效规避漏电风险,既保护了操作人员的安全,也避免了漏电流对测试设备和芯片的损坏,符合工业测试的安规要求。

三、谷易电子接地设计的核心优势与行业参考意义

谷易电子的接地设计,核心优势在于“精准适配场景+全域低阻抗+多功能协同”,其共地型测试座通过“接地弹簧探针+金属固持座+金属外框”的一体化架构,实现了接地、屏蔽、防静电的协同作用,既解决了高频、高压、敏感芯片测试中的干扰问题,又保障了测试安全与数据精准性。

从行业参考来看,谷易电子的应用案例表明,芯片测试座的接地设计需结合芯片类型、测试场景(高频/车规/精密),重点关注三个核心:一是接地回路的低阻抗,确保干扰信号与静电的快速导泄;二是接地结构与信号探针的隔离,避免串扰;三是接地的稳定性,适配高低温、振动等复杂测试环境。例如,高频芯片测试需强化接地屏蔽,敏感芯片测试需优化静电导泄效率,车规芯片测试需兼顾接地稳定性与安规要求,这些设计思路可为行业内其他测试座产品的接地设计提供参考。

芯片测试座中的接地,是保障芯片测试精准性、安全性、稳定性的核心环节,其本质是构建低阻抗的电流回流与干扰导泄通道,实现“抑制干扰、导泄静电、稳定电位、保障安全”的四大核心作用。谷易电子作为芯片测试座领域的标杆企业,其共地型测试座的专利设计与实际应用案例,充分体现了科学接地设计的重要性——通过一体化共地架构、精准的接地探针设计、场景化的优化调整,既解决了不同类型芯片测试中的接地痛点,又提升了测试效率与可靠性。

在线咨询

在线咨询

扫一扫关注官方微信

13823541376

13823541376