服务热线 13823541376

深圳市谷易电子有限公司

联系电话:13823541376

联系人:兰小姐

邮箱:sales@goodesocket.com

主营产品:定制测试座、老化测试座、弹片微针模组、memory测试座、测试夹具、BGA老化测试、QFN老化测试、Flash闪存测试、编程烧录座

发表时间:2026-03-16 10:29:23浏览量:206【小中大】

在芯片自动化测试设备(ATE)测试流程中,开短路测试(Open/Short Test,简称O/S测试)是芯片量产测试、成品验证的第一道核心关卡,也是保障芯片良率、规避后续测试资源浪费的关键环节。其核心测试原理依托芯片管脚内部集成的ESD(静电放电)防静电保护二极管,利用二极管单向导通特性及正向导通压降的固定范围,通过检测管脚对地、对电源端的导通状态,精准判断管脚是否存在开路、短路等制造缺陷。

一、芯片ATE测试中开短路测试(O/S测试)的定义与核心原理

芯片ATE测试中的O/S测试,本质是通过ATE设备的精密测量单元(PMU/PPMU),结合芯片管脚内置的ESD防静电保护二极管特性,检测芯片各管脚与地(GND)、电源端(VDD/VSS等)之间的电气连接完整性,判断管脚是否存在开路(Open)、短路(Short)故障,同时验证ATE测试系统与被测芯片(DUT)之间的物理连接可靠性,是芯片测试流程中耗时短、效率高、覆盖面广的基础测试项目。

其核心测试原理完全依托芯片本身的ESD防静电保护设计——为避免芯片管脚在生产、运输、测试过程中因静电放电受损,芯片每个管脚内部都会集成ESD保护二极管,且这些二极管均采用“双向保护”设计:即每个管脚与地(GND)之间、与电源端(VDD)之间,均反向并联一只ESD保护二极管(部分场景为双向二极管),形成“管脚-VDD二极管-VDD”“管脚-GND二极管-GND”的双重保护回路。在芯片正常工作时,这些二极管处于反向截止状态,不会影响管脚的信号传输或电气特性;而在O/S测试中,通过向管脚施加特定方向的微小电流,可使ESD保护二极管正向导通,利用其固定的正向导通压降范围,判断管脚的通断状态,具体原理拆解如下:

(一)ESD保护二极管的分布与特性基础

所有主流芯片(包括车规、高频、消费级芯片)的管脚内部,均遵循ESD保护设计规范,其ESD保护二极管的分布主要分为三种类型,适配不同管脚功能需求,也是O/S测试的核心依托:

管脚仅对地(GND)有ESD保护二极管:多见于简单信号管脚,二极管正极接GND、负极接管脚,反向截止时不影响信号传输,正向导通时可将管脚静电导泄至GND,O/S测试仅需检测管脚与GND的导通状态。

管脚仅对电源端(VDD)有ESD保护二极管:多见于电源管脚,二极管正极接管脚、负极接VDD,可防止管脚静电击穿电源回路,O/S测试重点检测管脚与VDD的导通状态。

管脚同时对地(GND)和电源端(VDD)有ESD保护二极管:这是最主流的设计(如GPIO管脚、高频信号管脚),两只二极管反向并联,分别实现对GND和VDD的静电保护,O/S测试需同时检测管脚与GND、管脚与VDD的导通状态,确保双重保护回路正常,同时判断管脚本身无开路、短路故障。

核心特性:ESD保护二极管(硅基)的正向导通压降(V_F)具有固定范围,通常在0.4V~0.8V之间(典型值0.6V~0.7V),这一固定特性是O/S测试判断管脚状态的核心依据——通过ATE设备施加微小测试电流,测量管脚与GND、VDD之间的电压,若电压在导通压降范围内,则说明管脚连接正常;若电压远超上限(如大于1.5V),则判定为开路;若电压接近0V(如小于0.2V),则判定为短路,这也是O/S测试的核心判断逻辑。

(二)O/S测试的核心判断逻辑(结合ESD二极管特性)

O/S测试的核心的是“施加微小电流→测量导通压降→对比阈值判断”,针对不同ESD二极管分布类型,测试逻辑略有差异,但均遵循二极管单向导通原理,具体如下(基于ATE设备PMU单元测试,常用测试电流为100μA、200μA,可根据芯片规格调整):

对地(GND)测试逻辑:向被测管脚施加负向微小电流(如-100μA,流入ATE设备为负电流),此时管脚与GND之间的ESD二极管正向导通,测量两者之间的电压。若电压在-0.8V~-0.4V范围内,说明管脚与GND连接正常;若电压低于-1.5V,判定为管脚对地开路;若电压高于-0.2V,判定为管脚对地短路。

对电源端(VDD)测试逻辑:向被测管脚施加正向微小电流(如+100μA,流出ATE设备为正电流),此时管脚与VDD之间的ESD二极管正向导通,测量两者之间的电压。若电压在0.4V~0.8V范围内,说明管脚与VDD连接正常;若电压高于1.5V,判定为管脚对VDD开路;若电压低于0.2V,判定为管脚对VDD短路。

对地+对电源端双重测试逻辑:针对同时具备双向ESD保护二极管的管脚,依次执行上述两种测试流程,只有两种测试的电压均在对应阈值范围内,才算管脚连接正常;若任一测试出现异常,均判定为管脚故障(开路或短路)。同时,为避免测试误差,需先将所有管脚接地,使芯片内部电路处于统一初始状态,消除其他管脚的干扰。

补充说明:测试过程中需设置合理的钳位电压(如±3V),钳位电压的绝对值需大于测试阈值(如1.5V),避免因电压被钳制导致“虚假通过”——若钳位电压设置过低(如1V),当管脚实际开路时,电压会被限制在1V,误判为正常状态,影响测试准确性。

二、芯片ATE测试中开短路测试(O/S测试)的核心痛点

O/S测试虽为基础测试,但测试精度直接影响芯片良率与后续测试效率,在实际ATE批量测试场景中,核心痛点主要集中在三点,也是测试方案设计的核心优化方向:

测试接触稳定性不足:ATE测试中,芯片通过测试座socket与ATE设备连接,若测试座探针接触不良、接触电阻过大,会导致导通压降测量失真,出现“虚假开路”“虚假短路”,误判芯片故障,增加测试成本;同时,探针磨损、氧化也会影响接触稳定性,尤其在批量测试(单日数万颗芯片)场景中,问题更为突出。

多管脚并行测试干扰:现代芯片管脚数量多达数百、数千个,为提升测试效率,通常采用PPMU架构实现多管脚并行测试,但并行测试时,相邻管脚的电流、电压会相互干扰,导致部分管脚导通压降测量偏差,尤其难以检测管脚之间(Pin-To-Pin)的短路故障——相邻管脚短路时,两者电位趋于相等,导通压降相近,测试结果易误判为正常。

场景适配性不足:不同类型芯片(车规、高频、精密芯片)的ESD保护二极管参数、管脚间距、封装形式(QFN、BGA、LGA等)存在差异,通用测试座与测试方案无法适配所有场景,易出现测试精度不足、芯片损坏等问题;同时,测试过程中产生的静电、干扰信号,也会影响ESD二极管导通压降的测量准确性。

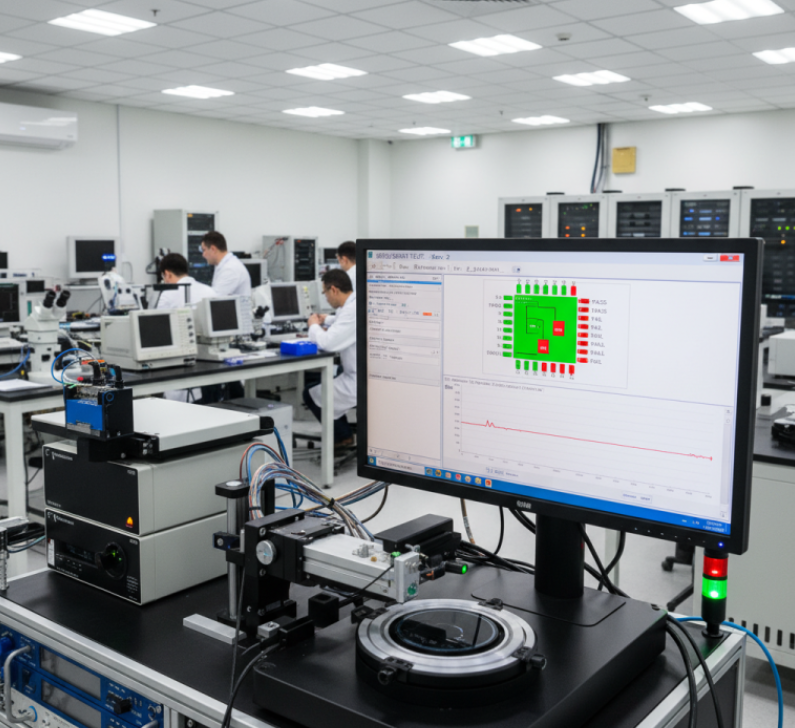

针对上述痛点,谷易电子作为IC测试座领域的专业解决方案提供商,深耕芯片ATE测试场景,推出定制化O/S测试座socket,结合其专利设计与实际应用案例,形成了适配多场景、高精度、高效率的O/S测试方案,有效解决了上述行业痛点。

三、芯片ATE测试中开短路测试方案(结合谷易电子测试座socket案例)

谷易电子聚焦芯片ATE开短路测试的核心需求,结合自身在测试座领域的技术积累(如共地架构专利、高精度探针设计),推出适配车规、高频、消费级等多类型芯片的O/S测试座socket,构建了“精准接触+抗干扰+场景适配”的一体化O/S测试方案,兼顾测试精度、效率与芯片安全性,以下结合其实际应用案例,详细解析方案核心设计与优势。

(一)方案核心设计:依托测试座socket,解决测试接触与干扰痛点

谷易电子O/S测试座socket的核心设计围绕“提升接触稳定性、抑制测试干扰”展开,结合芯片ESD保护二极管的测试特性,优化测试座结构与材质,为O/S测试提供可靠的连接载体,核心设计要点如下:

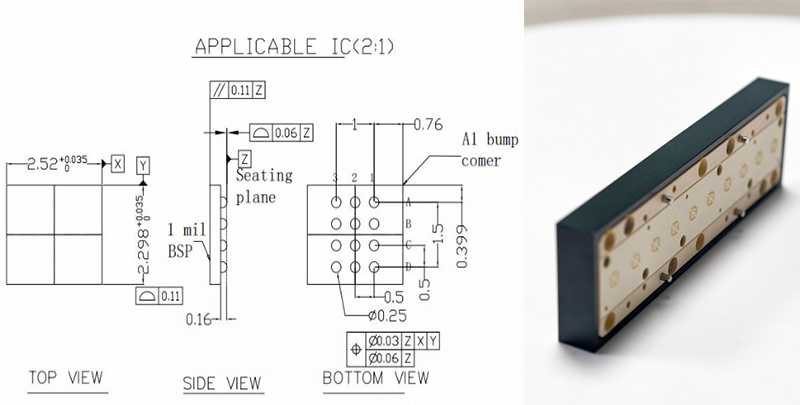

高精度探针设计,保障接触稳定性:采用定制化弹簧探针,探针表面采用镍钯金镀层(耐温200℃、耐磨耐腐蚀),接触电阻稳定在10mΩ以内,有效降低接触电阻对导通压降测量的影响;同时,探针采用浮动式设计,可补偿±30μm的芯片偏移量,确保探针与芯片管脚精准贴合,避免接触不良导致的测试失真。此外,探针弹簧弹力控制在20g~30g per Pin,既保证接触压力,又避免损伤芯片管脚与ESD保护二极管,适配批量测试场景,探针寿命可达30万次以上,大幅降低测试成本。

共地抗干扰架构,抑制并行测试干扰:借鉴谷易电子共地型测试座的专利设计(CN 117434304 A),测试座采用“金属外框+金属固持座+接地弹簧探针”的共地架构,形成统一接地网络,接地电阻稳定在10mΩ以内,可快速导泄测试过程中产生的干扰信号与静电,避免干扰信号影响导通压降测量。针对多管脚并行测试的Pin-To-Pin短路检测难题,谷易测试座支持“分组测试”模式,可将奇数、偶数管脚分组隔离,测试一组管脚时,将另一组管脚接地,强制短路管脚间形成电压差,有效避免误判,同时配合ATE设备的PPMU架构,实现多管脚并行测试,大幅提升测试效率——例如,针对100管脚芯片,并行测试仅需1毫秒,较串行测试效率提升100倍以上。

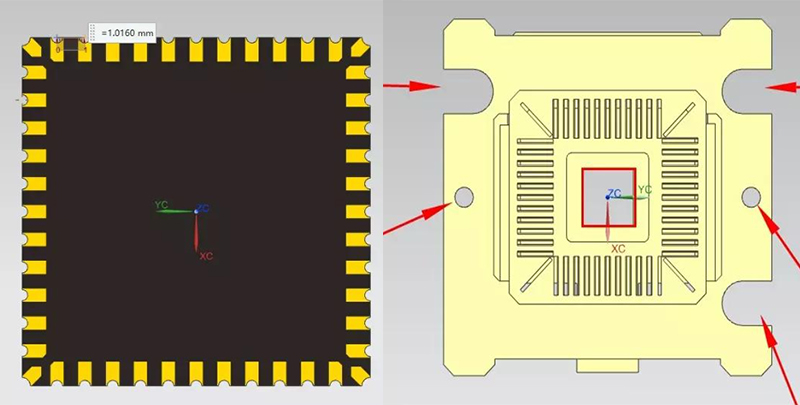

场景化适配设计,兼容多类型芯片:针对不同封装(QFN、BGA、LGA、QFP等)、不同管脚间距(0.3mm~1.27mm)的芯片,谷易电子提供定制化测试座socket,优化探针布局与导热结构,适配不同芯片的ESD保护二极管参数(如导通压降阈值、测试电流需求)。例如,针对车规芯片(如BMS MCU、AFE),测试座采用耐高温PBT工程塑料,适配-40℃~155℃的测试环境,同时强化静电防护,可快速导泄±15kV的静电,避免静电损坏ESD保护二极管,确保测试准确性;针对高频芯片(如5G射频芯片),测试座内置屏蔽套管,将信号探针与接地探针隔离,抑制高频干扰,避免导通压降测量偏差。

(二)方案测试流程(结合谷易测试座socket应用)

结合谷易电子O/S测试座socket的应用,芯片ATE开短路测试流程可分为4个步骤,兼顾效率与精度,适配批量测试场景,具体如下:

测试准备:将芯片精准放置于谷易O/S测试座socket中,通过测试座的定位结构(精准定位销)固定芯片,确保芯片管脚与测试座探针一一对应、紧密贴合;同时,将测试座与ATE设备的PMU/PPMU单元、接地端、电源端精准连接,通过测试座的共地架构,构建稳定的测试回路,消除环境干扰与静电影响。

初始状态校准:通过ATE设备将芯片所有管脚接地,使芯片内部电路处于统一初始状态,避免其他管脚的电位干扰;同时,利用谷易测试座的自检功能,检测探针接触状态,若出现接触不良,及时发出报警,避免后续测试误判。

分类型测试:根据芯片管脚的ESD保护二极管分布类型,执行对应的测试流程——对于仅对地/对电源端有ESD二极管的管脚,单独执行对应测试;对于双向保护的管脚,依次执行对地、对电源端测试,施加±100μA的测试电流,设置±3V钳位电压,通过ATE设备测量导通压降,与预设阈值(0.4V~0.8V、-0.8V~-0.4V)对比,判断管脚通断状态;多管脚测试时,采用分组并行测试模式,提升测试效率。

结果判定与反馈:测试完成后,ATE设备自动记录每根管脚的测试数据,结合谷易测试座的信号传输优势,确保数据无失真;若导通压降在阈值范围内,判定为合格;若出现开路、短路异常,自动标记故障管脚,反馈至测试系统,便于工作人员后续分析;测试完成后,测试座自动复位,准备下一颗芯片测试,实现批量自动化测试。

(三)谷易电子案例应用效果

某头部车规芯片厂商在BMS MCU芯片ATE批量测试项目中,采用谷易电子O/S测试座socket及配套测试方案,针对芯片管脚(同时对地、对电源端有ESD保护二极管)开展O/S测试,核心应用效果如下:

测试精度显著提升:通过谷易测试座的高精度探针与共地抗干扰设计,导通压降测量误差控制在±0.02V以内,虚假误判率降至10ppm以下,有效避免了因接触不良、干扰导致的误判,芯片良率检测准确性提升25%以上。

测试效率大幅优化:采用分组并行测试模式,配合谷易测试座的快拆设计,单日可完成20万颗芯片的O/S测试,较传统测试方案效率提升50%,大幅降低了批量测试的时间成本与人力成本。

场景适配性突出:该方案适配车规芯片的高温测试环境,同时兼容不同管脚间距的芯片,无需频繁更换测试座,测试故障率控制在5ppm以内;此外,测试座的静电防护设计,有效避免了测试过程中静电对ESD保护二极管的损坏,芯片测试损耗率降低30%。

此外,在5G射频芯片、消费级MCU芯片的ATE测试中,谷易电子O/S测试座socket同样实现了成熟应用,通过定制化探针布局与抗干扰设计,适配不同芯片的ESD保护特性,满足多样化O/S测试需求,成为行业内O/S测试的标杆方案之一。

四、O/S测试方案的核心优化方向与行业参考

结合谷易电子的案例实践,芯片ATE开短路测试方案的核心优化方向,需围绕“测试精度、效率、场景适配”三大维度展开,同时兼顾芯片安全性,具体可总结为三点:

强化接触稳定性:测试座的探针设计是核心,需采用高精度、高耐磨、低接触电阻的探针,配合浮动式结构,确保与芯片管脚的精准贴合,同时提升探针寿命,适配批量测试场景;

抑制测试干扰:通过共地架构、屏蔽设计,消除环境干扰、静电干扰及多管脚并行测试的相互干扰,同时优化测试参数(钳位电压、测试电流),避免虚假误判;

场景化定制:针对不同类型芯片的ESD保护特性、封装形式,提供定制化测试座与测试参数,确保测试方案的适配性,避免通用方案导致的测试精度不足、芯片损坏等问题。

从行业参考来看,谷易电子的应用案例表明,O/S测试的核心不仅是ATE设备的参数设置,更在于测试座socket的连接可靠性与抗干扰能力——测试座作为芯片与ATE设备的核心连接载体,其设计合理性直接决定O/S测试的精度与效率,而“高精度探针+共地抗干扰+场景化定制”的设计思路,可为行业内其他O/S测试方案提供重要参考。

芯片ATE测试中的开短路测试(O/S测试),是依托芯片管脚内部ESD防静电保护二极管的单向导通特性与固定正向导通压降,判断管脚与地、电源端之间通断状态的基础测试,是芯片良率控制、测试资源节约的关键环节。其核心逻辑是通过ATE设备施加微小测试电流,测量导通压降并与阈值对比,精准识别开路、短路故障,同时验证测试系统与芯片的连接可靠性。

谷易电子作为IC测试座领域的专业厂商,其O/S测试座socket通过高精度探针、共地抗干扰架构、场景化定制设计,有效解决了行业内接触不良、干扰、场景适配不足等痛点,结合实际应用案例,构建了高效、精准、可靠的O/S测试方案,既保障了测试精度,又提升了批量测试效率,降低了测试成本。

在线咨询

在线咨询

扫一扫关注官方微信

13823541376

13823541376